## **BACHELOR THESIS**

## Radek Zikmund

# NextGen SPICE – Electrical Circuit Simulation Library for .NET

Department of Distributed and Dependable Systems

Supervisor of the bachelor thesis: Mgr. Pavel Ježek, Ph.D.

Study programme: Computer Science

Study branch: Programming and Software Systems

| I declare that I carried out this bachelor thesis independencited sources, literature and other professional sources.                                                                                                                                         | tly, and only with the                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| I understand that my work relates to the rights and oblig<br>No. 121/2000 Sb., the Copyright Act, as amended, in partic<br>Charles University has the right to conclude a license agr<br>this work as a school work pursuant to Section 60 subsection<br>Act. | cular the fact that the element on the use of |

| In date signature of the au                                                                                                                                                                                                                                   | thor                                          |

Title: NextGen SPICE – Electrical Circuit Simulation Library for .NET

Author: Radek Zikmund

Department: Department of Distributed and Dependable Systems

Supervisor: Mgr. Pavel Ježek, Ph.D., Department of Distributed and Dependable

Systems

Abstract: The goal of this thesis was to create an extensible library for simulating electrical circuits for the .NET platform, which could be used in broad contexts like development of educational programs or applications that use evolutionary algorithms to evolve electrical circuits. Our library is inspired by the family of SPICE programs developed at University of California, Berkeley.

Initial version of our library implements the transient analysis of electrical circuits and supports basic devices like voltage and current sources, resistors, capacitors, inductors, but also semiconductor diode and BJT transistor devices. Our library is designed in such a way that both new circuit devices and circuit analyses can be added in future versions.

Other features of our library include importing circuits or their parts from the industry standard SPICE netlists and ability to modify circuit parameters during the simulation. In this thesis, we also investigate using double-double precision type to improve convergence during the simulation.

We also implement a simple SPICE-like console application to allow our simulation library to be used from command line.

Keywords: Electrical circuit simulation SPICE .NET Library

Název práce: NextGen SPICE – knihovna pro simulaci elektrických obvodů pro .NET

Autor: Radek Zikmund

Katedra: Department of Distributed and Dependable Systems

Vedoucí bakalářské práce: Mgr. Pavel Ježek, Ph.D., Katedra distribuovaných a spolehlivých systémů

Abstrakt: Cílem této práce bylo vytvořit rozšiřitelnou knihovnu pro simulaci elektrických obvodů pro platformu .NET, která by byla uplatnitelná v širokém kontextu, jako je vývoj výukových programů nebo aplikací využívajících evolučních algoritmů pro evoluci elektrických obvodů. Naše knihovna je inspirována rodinou SPICE programů vyvíjených na Kalifornské univerzitě v Berkeley.

Počáteční verze naší knihovny implementuje transientní analýzu elektrických obvodů a podporuje základní součástky jako zdroje napětí a proudu, rezistory, kondenzátory a cívky, ale také polovodičové diody a BJT transistory. Naše knihovna je navržena takovým způsobem, že je možné v budoucích verzích knihovny přidat jak nové součástky, tak nové typy analýz.

Další vlastnosti naší knihovny zahrnují importování obvodů nebo jejich částí v průmyslově standardním SPICE netlist formátu a možnost upravovat parametry součástek během simulace. V této práci také prověřujeme použití typů s přesností double-double pro zlepšení konvergence během simulace.

Také jsme implementovali jednoduchou SPICE-like konzolovou aplikaci abychom umožnili používání naší simulační knihovny z příkazové řádky.

Klíčová slova: Simulace elektrických obvodů SPICE .NET Knihovna

I would like to thank my supervisor Mgr. Pavel Ježek, Ph.D. for his time, patience and the advice he gave me during our consultations. Also, special thanks go to my family, friends and everybody who supported me and helped me during my studies.

# Contents

| 1 | Intr | oduction                                       |

|---|------|------------------------------------------------|

|   | 1.1  | The Berkeley SPICE                             |

|   | 1.2  | Present-day Situation                          |

|   | 1.3  | Use of Circuit Simulators Outside Industry     |

|   | 1.4  | Reimplementation of SPICE for .NET             |

|   | 1.5  | Goals                                          |

|   |      |                                                |

| 2 |      | SPICE Netlist Syntax                           |

|   | 2.1  | General Syntax                                 |

|   |      | 2.1.1 Number Fields                            |

|   |      | 2.1.2 Name Fields                              |

|   |      | 2.1.3 Comments                                 |

|   | 2.2  | Data Statements                                |

|   |      | 2.2.1 Resistor                                 |

|   |      | 2.2.2 Capacitor                                |

|   |      | 2.2.3 Inductor                                 |

|   |      | 2.2.4 Input sources                            |

|   |      | 2.2.5 Controlled Sources                       |

|   |      | 2.2.6 Diode                                    |

|   |      | 2.2.7 BJT Transistor                           |

|   |      | 2.2.8 Subcircuits                              |

|   |      | 2.2.9 Summary of the Device Statements         |

|   | 2.3  | Control Statements                             |

|   | 2.3  |                                                |

|   |      |                                                |

|   | 0.4  | 2.3.2 .TRAN Statement                          |

|   | 2.4  | Output Statements                              |

|   | 2.5  | Netlist File Structure                         |

|   | 2.6  | Circuit Topology Constraints                   |

| 3 | Imp  | elementation Analysis 3                        |

|   | 3.1  | Initial Organisation of the library            |

|   |      | 3.1.1 Overview of SPICE Simulator Workflow     |

|   |      | 3.1.2 Separating Circuit Analyses              |

|   |      | 3.1.3 Devices and Device Models                |

|   |      | 3.1.4 Splitting to Multiple Assemblies         |

|   | 3.2  | NextGenSpice.Core                              |

|   | 5.2  | 3.2.1 Representation of the Circuit            |

|   |      | •                                              |

|   | 2.2  |                                                |

|   | 3.3  | SPICE Netlist Parser                           |

|   | 3.4  | Double-double and Quad-double Arithmetic       |

|   | 3.5  | NextGenSpice.LargeSignal                       |

|   |      | 3.5.1 Transient Analysis Overview              |

|   |      | 3.5.2 Choice of Equation System Formulation 4  |

|   |      | 3.5.3 Equation System Abstraction 4            |

|   |      | 3.5.4 Choice of Numerical Integration Method 4 |

|   |                | 3.5.5         | Choice of Timestep                                 | 49        |

|---|----------------|---------------|----------------------------------------------------|-----------|

| 4 | Dev            | eloper        | Documentation                                      | 51        |

|   | 4.1            | Comp          | ilation                                            | 52        |

|   | 4.2            | NextC         | GenSpice.Core                                      | 52        |

|   |                | 4.2.1         | Circuit Description                                | 52        |

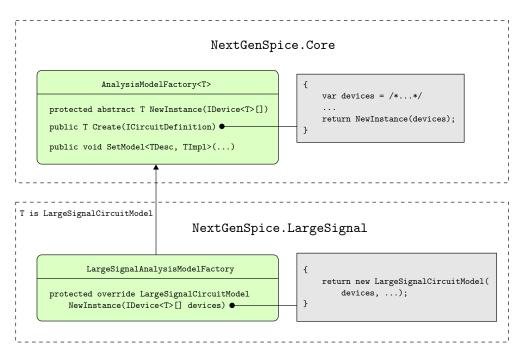

|   |                | 4.2.2         | General Analysis Implementation Design             | 53        |

|   |                | 4.2.3         | Analysis Model Creation                            | 54        |

|   |                | 4.2.4         | Discovering Analysis Model Implementations         | 55        |

|   | 4.3            | NextC         | GenSpice.Parser                                    | 55        |

|   |                | 4.3.1         | Tokenizing                                         | 56        |

|   |                | 4.3.2         | Processing Statements                              | 56        |

|   | 4.4            | NextC         | GenSpice.LargeSignal                               | 57        |

|   | 4.5            |               | GenSpice.Numerics and NextGenSpice.Numerics.Native | 59        |

|   |                | 4.5.1         | Equation System Implementation                     | 59        |

|   | 4.6            | NextO         | GenSpice                                           | 60        |

|   | 4.7            |               | oxRunner                                           | 60        |

|   | 4.8            |               | Test Projects                                      | 60        |

| 5 | Use            | r Doci        | umentation - Library                               | 61        |

| • | 5.1            |               | ials                                               | 61        |

|   | 0.1            | 5.1.1         | Calculating DC Bias of the Ciruit                  | 61        |

|   |                | 5.1.2         | Performing Transient Analysis                      | 63        |

|   |                | 5.1.3         | Loading Circuits from Netlists                     | 65        |

|   |                | 5.1.4         | Defining a Subcircuit in Source Code               | 66        |

|   | 5.2            |               | GenSpice.Core                                      | 67        |

|   | 5.4            | 5.2.1         | Creating the Circuit Description                   | 67        |

|   |                | 5.2.1 $5.2.2$ |                                                    | 67        |

|   |                |               | Supported Circuit Devices                          |           |

|   | F 9            | 5.2.3         | Creating Analysis-Specific Circuit Models          | 68        |

|   | 5.3            |               | GenSpice.Parser                                    | 69<br>70  |

|   | 5.4            |               | GenSpice.LargeSignal                               | 70        |

|   |                | 5.4.1         | Accessing the Computed State                       | 70        |

|   |                | 5.4.2         | Modifying the Device Parameters                    | 70        |

|   |                | 5.4.3         | Changing the Integration Method                    | 71        |

| 6 | Ext            | _             | g the Library                                      | <b>75</b> |

|   | 6.1            | Addin         | g New Circuit Devices                              | 75        |

|   |                | 6.1.1         | Adding Device Description                          | 75        |

|   |                | 6.1.2         | Adding Large-Signal Device Implementation          | 75        |

|   | 6.2            | Exten         | ding the Parser                                    | 76        |

|   |                | 6.2.1         | Adding New Device Processors                       | 76        |

|   |                | 6.2.2         | Adding New Model Types                             | 78        |

|   | 6.3            | Exam          | ple: Adding a Diode Device                         | 78        |

|   |                | 6.3.1         | Creating a Diode Device Definition                 | 79        |

|   |                | 6.3.2         | Parsing diode statements                           | 79        |

|   |                | 6.3.3         | Implementing Large-Signal Diode Logic              | 81        |

| 7 | $\mathbf{Use}$ | r Doci        | umentation - Standalone Application                | 83        |

| 8             | Results 8       |                                          |    |

|---------------|-----------------|------------------------------------------|----|

|               | 8.1             | Comparison of Precision Type Performance | 87 |

|               | 8.2             | Comparison with Ngspice Simulator        | 90 |

|               | 8.3             | Comparison with SpiceSharp               | 91 |

|               | 8.4             | Summary                                  | 94 |

| Co            | nclu            | sion                                     | 95 |

| Bi            | bliog           | raphy                                    | 99 |

| $\mathbf{At}$ | Attachments 103 |                                          |    |

## 1. Introduction

The process of designing electrical circuits consists of several stages, starting with detailed specification from the customer that provides all necessary requirements, and ending with a working prototype of the final product. Intermediate stages include prototyping circuits using a construction base commonly referred to as breadboard, which is is often very slow and for complex integrated circuits even impossible. The task has been made easier with the invention of electrical circuit simulation programs, which allow quick circuit prototyping without the need of soldering iron.

## 1.1 The Berkeley SPICE

One of the most successful circuit simulators is the SPICE program<sup>1</sup> developed at EECS Department of the University of California, Berkeley. The original SPICE1 program is implemented in FØRTRAN language and was released in 1971. Its popularity quickly rose and few years later, Berkeley released SPICE2 with many performance improvements and model enhancements. SPICE programs developed at Berkeley heavily influenced development of future circuit simulation software, and we will describe them in more depth in following sections.

#### **Netlists**

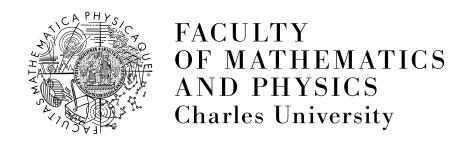

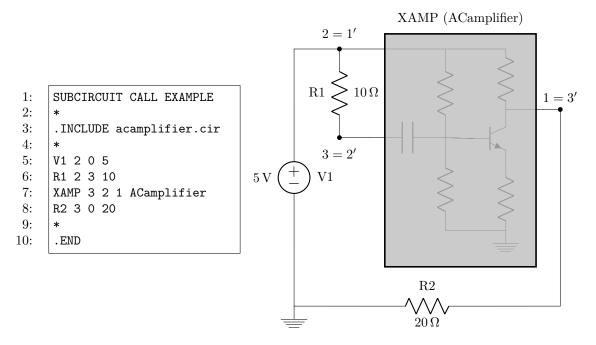

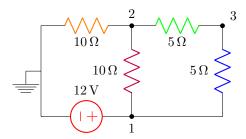

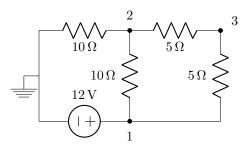

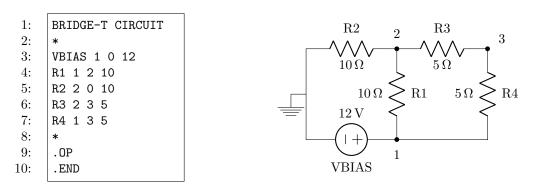

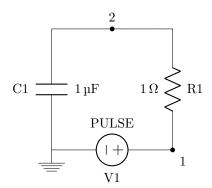

Early versions of SPICE did not operate in interactive mode, therefore the input files contained both data and instructions for processing. These input files conventionally have .cir extension, and the contained circuit description is called netlist. A simple example of netlist is shown on the figure 1.1 on the left, with a schematic of corresponding circuit on the right. The meaning of individual lines of the netlist is explained in the next paragraph.

Figure 1.1: Example .cir netlist file, reproduced from The SPICE Book [1] and corresponding circuit schematic

The netlist in figure 1.1 is divided into three sections, separated by empty comment on lines 2 and 8. The first section of the netlist contains the name of circuit, then follows a second section with definitions of five devices: one voltage

<sup>&</sup>lt;sup>1</sup>The name SPICE stands for Simulation Program with Integrated Circuit Emphasis.

source and four resistors. The type of each device is inferred from the first letter of its name. Each definition contains list of connected nodes and value of source voltage or resistor's ohmic resistance, respectively. Node 0 is special, because it corresponds to the ground and must be present in every circuit (detailed description of SPICE netlists syntax and rules for validating the circuit will be presented later in chapter 2). In the last section of the file, there is an .OP statement, which instructs the simulator to perform an operating point analysis to find stable values of node voltages of the circuit, and .END statement denoting the end of netlist. This syntax for describing electrical circuits became an industry standard during the 1970s, and most modern circuit simulators still recognize it.

When SPICE2 is run with the previously shown netlist file, it first reads all components, checks syntax and topology rules for the circuit, and then runs the operating point analysis – computes node voltages and current through the VBIAS voltage source. After that, it prints a rather verbose report, as shown in figure 1.2. First, description of the input circuit is repeated back to the user (only part of the description is shown in the figure for brevity, in top half in grey), then follows a list of node voltages and then currents flowing through voltage sources.

```

****** 03/19/91 ******* SPICE 2G.6 9/21/84 ****** 06:47:36 *******

1:

2:

3:

BRIDGE-T CIRCUIT

4:

CIRCUIT DESCRIPTION

5:

6:

7:

8:

9:

VBIAS 1 0 12

10:

11:

12:

13:

****** 03/19/91 ******* SPICE 2G.6 9/21/84 ****** 06:47:36 *******

14:

15:

BRIDGE-T CIRCUIT

16:

SMALL SIGNAL BIAS SOLUTION

17:

TEMPERATURE = 27.000 DEG C

18:

19:

20:

21:

NODE

VOLTAGE

NODE

VOLTAGE

NODE

VOLTAGE

NODE

VOLTAGE

22:

23:

1)

12.0000

2)

8,0000

(

3)

10.0000

24:

VOLTAGE SOURCE CURRENTS

25:

26:

NAME

CURRENT

27:

28:

VBIAS

-8.000E-01

29:

30:

TOTAL POWER DISSIPATION 9.60E+00 WATTS

```

Figure 1.2: Output of SPICE2G.6 for the example netlist file, from The SPICE Book [1]

#### Macromodels

One of the most useful features of SPICE is the ability to define custom subcircuits, called *macromodels*, composed from devices already integrated in the simulator, or other macromodels. Circuits can be then decomposed to individual subcircuits, similarly to how a computer program's source code can be decomposed into individual functions. One macromodel can then represent a complex real-life device, e.g. an amplifier, and can be simply reused throughout the whole circuit.

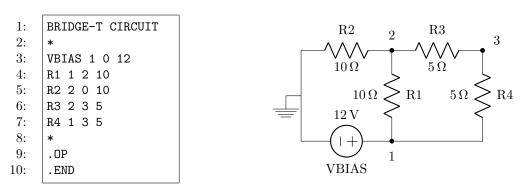

This allows device manufacturers to provide a SPICE netlists with macromodels that accurately model their devices. An example of such manufacturer is Analog Devices, macromodels for their products can be downloaded from their webpage, screenshot of which is shown in figure 1.3. The manufacturer's customers can then use these macromodels in their simulators to model behavior of circuit that uses the manufacturer's products.

Figure 1.3: Website of Analog Devices, where SPICE macromodels can be downloaded.

Today, vast libraries containing hundreds of SPICE netlists with macromodels exist, and therefore it is a very important feature of any modern circuit simulator to be able to import macromodels from these netlists.

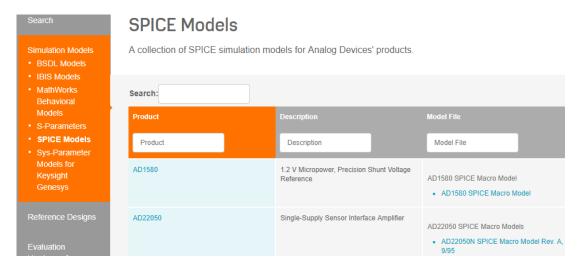

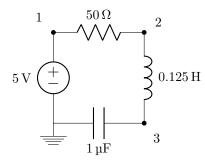

Manufacturer-supplied macromodels are often very complex and the netlists are too long to be shown here. Instead, the use of macromodels is demonstrated on a simple macromodel for AC coupled amplifier. The netlist description is shown in figure 1.4. Very important part of the definition is the opening .SUBCKT statement, which denotes start of the subcircuit description, and specifies its name and terminal nodes which will serve as an interface to the outer circuit. After that follows description of the devices that constitute the macromodel, and finally, the subcircuit definition is ended by .ENDS statement. The subcircuit in the figure is named ACamplifier and terminal nodes are 1, 2 and 3. Other nodes (excluding 0, which is global ground node) and all devices used between the .SUBCKT and .ENDS statement are strictly local to the subcircuit and are not visible to the outside circuit.

Figure 1.4: Simple macromodel example for AC coupled amplifier [2], and corresponding circuit schematic, adapted from a 5Spice tutorial by Richard P. Andresen

Such a macromodel can then be used by providing nodes for terminal connections. In SPICE netlist, a macromodel is represented by a device with name staring with an X. The actual macromodel to be used is specified as the last argument in the device statement. An example of a circuit that uses the ACamplifier macromodel is shown in figure 1.5. The macromodel definition is inleuded from a separate file, similarly to the #include preprocessor directive in C or C++. In the actual circuit, the macromodel is represented by the XAMP device. Nodes 3, 2 and 1 are mapped onto the nodes 2, 1 and 3 from the macromodel description.

Figure 1.5: Illustrative example of circuit that uses macromodel from figure 1.4

#### From SPICE2 to SPICE3

SPICE2 was not the last SPICE program developed by Berkeley. With the increasingly more popular UNIX-based operating systems, it was possible for programs to be more interactive. Andrei Vladimirescu states in The SPICE Book [1] that SPICE2 was 'a FORTRAN batch program and was difficult to modify and limited in its potential use of C-shell utilities'. These limitations led Berkeley to start development of SPICE3 in the C programming language during the 1980s. In addition to more detailed models and improved numerical accuracy, SPICE3 was to support interactive mode, which allowed separating circuit description and commands for requesting circuit analysis.

Unfortunately, the development was in the end left to a handful of students due to limited financial resources. The first release of SPICE3 was very buggy and was not backward compatible with SPICE2. This was a big problem, because hundreds of commonly used macro-models would have to be rewritten before they could be used in SPICE3. Even though most incompatibility issues were fixed in later releases, SPICE3 did not completely replace SPICE2 and both coexist as two standards for circuit simulations, with the SPICE2 one being subset of SPICE3 and therefore more portable.

## 1.2 Present-day Situation

SPICE programs developed at Berkeley strongly influenced the development of circuit simulators used in industry. Because of the vast existing libraries of SPICE netlist files for various circuits, most circuit simulators either use the syntax which is a superset of the one used in SPICE, or provide some other way of importing circuits from the standard SPICE format.<sup>2</sup> There is even a categorization of circuit simulators based on the backward compatibility with Berkeley SPICE programs. Ron Kielkowski summarizes this in Inside SPICE [3] as follows:

Of all the analog circuit simulation tools available, the overwhelming majority of them are SPICE-like or SPICE-compatible. SPICE-like means a simulator is capable of producing an analysis result similar to the SPICE result for a given circuit, although they many not be able to read a standard SPICE circuit. SPICE-compatible means a simulator can read a SPICE circuit file and produce the result in standard SPICE2G.6 form.<sup>3</sup>

This only reinforces the idea that the backward compatibility with the original SPICE programs is an important feature of circuit simulators.

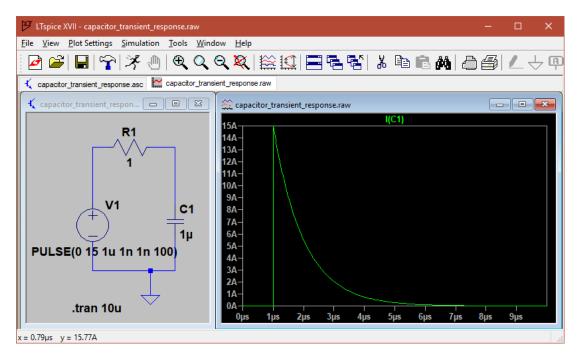

Today's circuit simulating programs commonly include a graphical tool for editing circuits and plotting the simulation results. Instead of writing netlist files by hand, circuits are edited using drag-and-drop operations. One such program is LTspice [4], whose graphical user interface is shown in figure 1.6.

<sup>&</sup>lt;sup>2</sup>Example of a simulator which does not support SPICE syntax directly is QUCS simulator, which provides a tool for transforming the netlist in SPICE format into the QUCS format.

<sup>&</sup>lt;sup>3</sup>Result shown in figure 1.2 is an example of such standardized output.

Figure 1.6: Graphical user interface of LTspice

## 1.3 Use of Circuit Simulators Outside Industry

Berkeley SPICE programs were designed from the start to be used as an aid for integrated circuit designers. The same can be said about the SPICE's successors that are used today. However, thanks to significant increase in computational power, it is now possible to use circuit simulators in other contexts too. There is an ongoing research on use of evolutionary algorithms to evolve circuit parameters and even circuit topology. For example, in 2016, Rojec et al. successfully evolved a passive low-pass filter [5]. Also, computers and other interactive equipment are often used for educational purposes in schools, so a circuit simulator can be used as part of an educational program intended for high school or university students.

We have in mind creating such applications, and their development would be greatly simplified if there was a suitable circuit simulation library. We would essentially like the simulator to allow what we will call a *live simulation*. For example, in a potential educational program, we would like to allow user (student) to e.g. flip switches or manipulate parameters of individual devices (e.g. resistances on the resistors), and hence provide an interactive experience. Also, circuit evolution applications could also make use of the possibility to simply manipulate circuit parameters. The first step of development of these applications would be finding and preparing such simulation library.

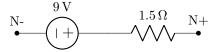

Since such applications would be used primarily for a cademic or educational purposes, it is desired that these programs be easy to develop, maintain, and – in case of educational applications – support multiple platforms. For these reasons it is probable that these applications would not be developed in some low level language like C++, but rather a more higher level language. One such language, C#, is part of the .NET developer platform, which is widely used in desktop application development. In recent years, .NET expanded to other platforms as well and would be therefore our choice in development of said applications. As we have written earlier, SPICE programs and their descendants were designed mainly to be an aid for electrical engineers. As a consequence, they can only perform off-line simulation, where the simulated period needs to be set explicitly before the simulation starts. During our research we did not find any simulator which would allow the simulation to be continued where it left off.<sup>4</sup> Furthermore, most simulators do not offer binary API for other programs to use, which means that the communication with the simulator needs to be done through the SPICE netlist files. One simulator which stands out is ngspice [6], which exposes a set of functions that allow manipulation of the simulator from an external program. The ngspice API does not require the input file to be written on disk, but we are still required to convert a simulated circuit into the netlist description, which is then passed to ngspice using a char\*\* pointer.<sup>5</sup>

Existing simulator programs therefore are not suitable for our purpose, we should search among the existing simulator libraries. At the time of assignment of this thesis, there was no implementation of a circuit simulation library for .NET Framework.<sup>6</sup> There are libraries for Python, for example PySpice [9] and PyOPUS [10] – but these two libraries rely on standalone simulators (namely ngspice [6] and HSPICE [11]) to do the simulation and therefore share the same limitations. There is also JSpice [12] library for Java, which implements it's own simulation engine, but just like other simulators requires the user to specify simulation duration beforehand.

Possible solution to the problems of using present-date simulator programs or libraries is rewriting an existing circuit simulator in .NET Framework and make necessary changes to the interface for our purpose. Berkley SPICE3 is still considered a reference simulator program, and since it is open source and freely available on the website of University of California, Berkeley [13], we will examine the possibility of rewriting it in .NET in the next subsection.

#### Rewriting SPICE3 for .NET, a Viable Option?

The SPICE3 was written in now non-standard C K&R norm, because the development started years before the first ANSI norm was released in 1990. Due to the nature of the C language, many parts of the simulator are very fragile and hard to maintain from today's perspective. Consider snippet in figure 1.7 taken from the last SPICE3 release (version 3f.5 from 1993). It contains a function which loads instances of voltage controlled current source devices to the circuit equation matrix. This function is just one example from the set of functions that must exist for each device in SPICE3 implementation. Other such functions include methods for model updating and data printing.

There are many points worth mentioning. In the declaration of the VCCSload function, the function parameters are specified by name only (line 3). The type of each parameter is then specified separately (lines 4–5). This is the main

<sup>&</sup>lt;sup>4</sup>For simple circuits, this can be achieved by setting the initial conditions of the circuit devices to be equal to the state of the circuit at the end of previous simulation, and recomputing the parameters for input sources (like phase offset and pulse delay). However, it is impossible to get or let alone set state of a device inside a subcircuit (the X device).

<sup>&</sup>lt;sup>5</sup>For more details, see section 19.3 (Shared ngspice API) in ngspice user manual [7].

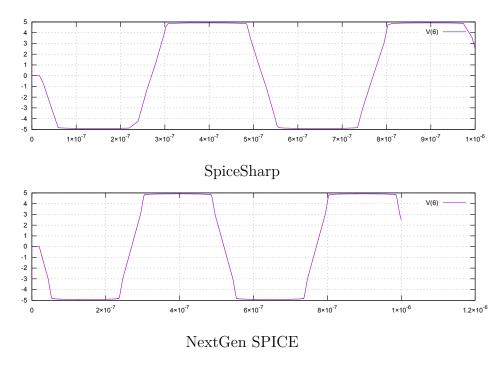

<sup>&</sup>lt;sup>6</sup>At the time of writing, there is the SpiceSharp [8] library, whose development started shortly after that of NextGen SPICE.

```

1:

/*ARGSUSED*/

2:

int

3:

VCCSload(inModel,ckt)

4:

GENmodel *inModel;

5:

CKTcircuit *ckt;

6:

/* actually load the current values into the

7:

* sparse matrix previously provided

8:

*/

9:

{

10:

register VCCSmodel *model = (VCCSmodel *)inModel;

11:

register VCCSinstance *here;

12:

13:

/* loop through all the source models */

for( ; model != NULL; model = model->VCCSnextModel ) {

14:

15:

16:

/* loop through all the instances of the model */

17:

for (here = model->VCCSinstances; here != NULL ;

18:

here=here->VCCSnextInstance) {

19:

20:

*(here->VCCSposContPosptr) += here->VCCScoeff ;

21:

*(here->VCCSposContNegptr) -= here->VCCScoeff ;

*(here->VCCSnegContPosptr) -= here->VCCScoeff

22:

23:

*(here->VCCSnegContNegptr) += here->VCCScoeff ;

24:

}

25:

}

26:

return(OK);

27:

}

```

Figure 1.7: Code snippet from spice3f5/src/lib/dev/vccs/vccsload.c

characteristic of the K&R C. In the ANSI C, equivalent declaration would be VCCSload(GENmodel \*inModel, CKTcircuit \*ckt).

Next thing to notice is the pointer casting on line 10 – the inModel parameter is cast to pointer to the concrete type of the device that is being loaded. Practices like this are very common in C code due to the lack of higher-level language features like inheritance and polymorphism. Also, because no type checking occurs in C during pointer casting, it can be a source of hard-to-debug errors if the target object is of different type.

Lines 10 and 11 also include the register keyword, which used to be a hint for the compiler to store the variable in a CPU register for faster access. This keyword is now deprecated, because modern compilers can do a better job at assigning variables to registers than a human programmer.

The last point worth noticing is the usage of pointers when accessing the equation matrix (lines 20 to 23). C# does allow usage of pointers in so called  $unsafe\ code\ block$ , but they affect the performance of garbage collector, and should be used carefully.

Although it is possible to extend SPICE3 with new circuit devices by following instructions from Thomas Quarles, author of SPICE3 [14], adding new analysis

types requires modifying method tables for all existing devices and other crucial parts of the simulator, and thus is time consuming and error-prone.

SPICE3 code also makes heavy use of #define #ifdef and other preprocessor directives which make the source code less readable. In combination with long functions and scarce source code documentation available (for an example, see file spice3f5/src/lib/ckt/dctran.c), rewriting the simulator is a very hard task requiring in-depth analysis and understanding of the simulator internals.

Overall, the programming style used in SPICE3 implementation is very different from the style used in modern object oriented programming languages like C#, and its code is not suitable for simple one-to-one translation from C to C#.

#### Main thesis goal

Because of reasons listed so far in this chapter, computer programs which would as part of their functionality perform live simulation of electrical circuits would have to implement their own simulator engine. As the primary goal of this thesis, we would like to simplify development of such applications by implementing such circuit simulator from the ground up in the form of portable .NET library. We will specify our requirements on the library in the next section.

## 1.4 Reimplementation of SPICE for .NET

Modern circuit simulators can do many types of circuit analyses and support many types of circuit devices. Because implementing range of functionality comparable to these programs would be out of scope of this thesis, we have selected a reasonable subset to be implemented, which is described in following subsection in greater detail. However we would like to be able to implement other features in the future without affecting user's code. We would therefore have to design the library to be appropriately extensible.

#### Requirements on the Library

We would like the library to be usable in broad contexts. Since .NET is now supported on many platforms, including Windows, Linux, and even mobile devices (Android, iOS and Windows Mobile), the library should be targeted to .NET Standard to make it maximally portable and usable on any .NET platform.

Our primary goal in the library will be supporting live simulation, as we described earlier. This essentially requires implementing equivalent of *transient analysis* of the SPICE simulator. However, the simulator should perform the individual timesteps on demand and allow making reasonable changes to the circuit devices like flipping switches, changing resistances, changing values of voltage and current sources.

The transient analysis requires so called *large-signal* models of the simulated devices, which are also used by other types of SPICE-like analyses, like DC Sweep Analysis. DC Sweep analysis calculates the circuit states for range of values for a certain circuit parameter (like resistance of a resistor or value of voltage/current source). Because we already wish to support changing parameters between individual timesteps, our library will also support DC Sweep analysis.

We would like to design our library so that it could potentially support the same set of devices as the SPICE simulators. However, the implementation of all SPICE devices is quite complex and would be out of scope of this thesis. We have therefore decided to implement the basic devices like ideal resistor, voltage or current sources, capacitor and inductor. Also, to demonstrate that even the complex semiconductor devices can be implemented, we will implement diode and BJT transistor devices as well. These two devices are reasonably simple to implement and at the same time complex enough to demonstrate the capabilities of the simulator. Because SPICE is considered the reference circuit simulator implementation, we would implement these devices using the same mathematical models that are used in the SPICE simulators.

In the future, we would also like to add other types of circuit analyses – such as AC frequency sweep analysis – and new devices, and even allow users of our library to implement their own. The library should be therefore extensible without modifying the core library's source code.

To provide academic researchers a way to test newly developed models and computational techniques, the library should be widely configurable, and preferably open-source, to allow its users to contribute to the library's development.

Also, since there already exist vast libraries of spice circuits and subcircuits with macromodels described in the industry-standard SPICE netlist syntax, we would like to our library to support importing circuits from SPICE netlists. We will therefore provide SPICE netlist parser as part of our library.

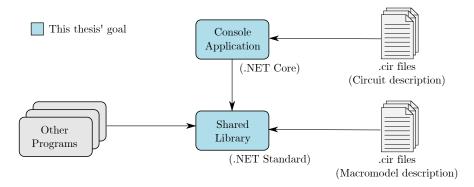

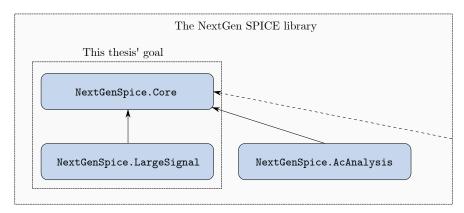

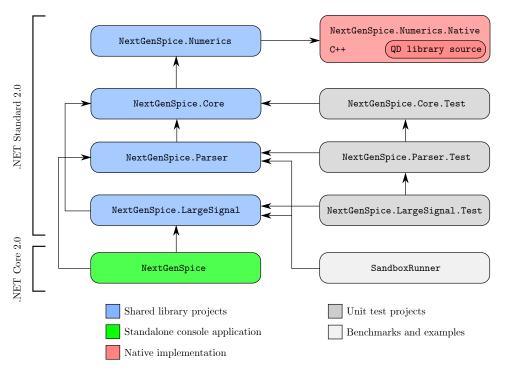

Since we have to recognize great portion of SPICE netlist syntax in order to parse macromodel descriptions, with little additional work we could implement the parser to recognize control statements for requesting individual circuit analyses (like the .0P statement we saw in figure 1.1). This would allow us to create a console application similar to the original SPICE and therefore allow capabilities of the library to be used in a standalone fashion using the SPICE netlist syntax. Since .NET Standard cannot be used to develop console applications, we require that the console application requires the next smallest set of API: .NET Core. Figure 1.8 shows the expected relationship between the simulator, console application and other programs that would use the simulator – parts in blue will be implemented as part of this thesis.

Figure 1.8: Dependency diagram for NextGen SPICE and other programs

#### Nonconvergence Due to Low Precision

Implementing any kind of simulation software means choosing an appropriate mathematical model for given problem domain and, subsequently, suitable representation of the problem in computer memory. Representing real numbers is integral part of every physics simulation engine.

To achieve fast simulations, developers have to choose between representations having hardware support on the target platforms, which leaves them with IEEE 32-bit (single) and 64-bit (double) floating-point types.

Most of the common circuit simulators use type double with approximately 15 decimal digits precision. Due to the large dynamic range of the circuit variables, this leads to significant truncation errors when equation system coefficients differ in more than 15 orders of magnitude.

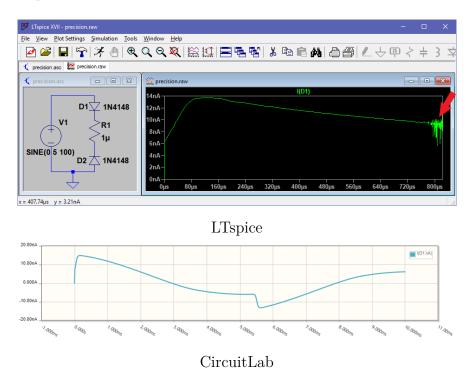

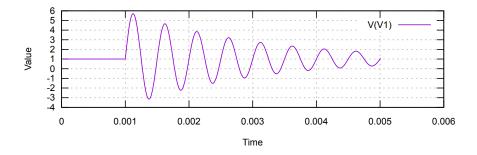

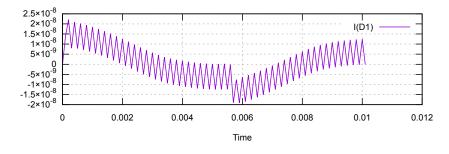

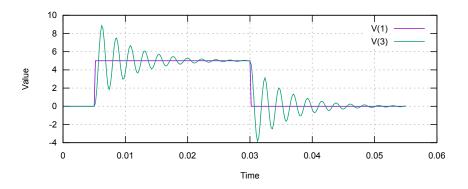

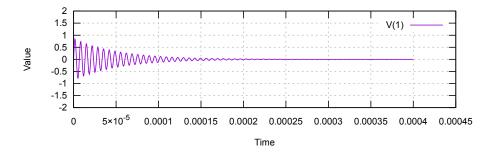

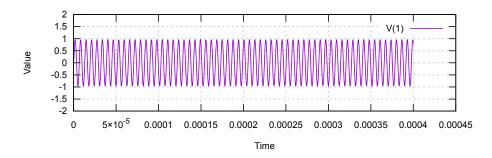

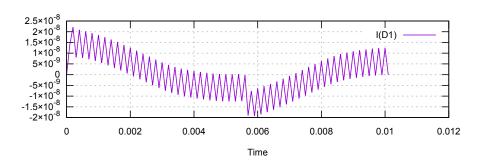

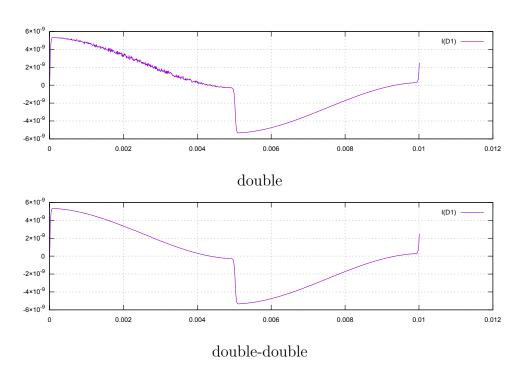

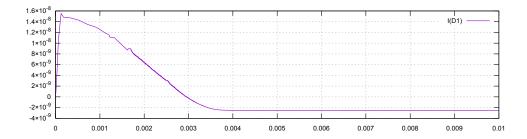

Coefficient differences of this magnitude may commonly occur when resistors with very small resistance values are used. Mike Robbins, one of the authors of online circuit simulator CircuitLab, provides a simple example of such ill-conditioned circuit in an article on their website [15]. This circuit along with the (partial) result plot from LTspice can be found in the upper part of figure 1.9. Notice the noise at the end of the simulated period emphasized by the red arrow. The lower part contains result of the same circuit in CircuitLab simulator.<sup>7</sup>

Figure 1.9: Example ill-conditioned circuit, and example results form LTspice (top, incomplete), and CircuitLab (bottom), adapted from [15]

The noise in the plot on the figure is caused by the  $1\mu\Omega$  resistor in the circuit. In the comment section under the article, Robbins writes that such small resistors

<sup>&</sup>lt;sup>7</sup>Keen reader might notice differences between the plot of CircuitLabs simulator results shown in this thesis and the one in the referenced article. These are due to the fact that CircuitLab uses slightly different model parameters for 1N4148 diode than LTspice. Plot shown in this thesis was obtained using the model parameters extracted from LTspice model library.

are not physical, meaning that they do not correspond to physical resistor devices, but can be produced during automated macromodel construction. Use of this small resistor led to too-big differences between the equation coefficients, which in turn led to significant truncation errors and produced noise seen in the plot. This noise later leads to nonconvergence of the equation solution. Nonconvergence of the solution is a rather technical issue, and essentially means that the simulator cannot determine the state of the circuit after the next timestep.<sup>8</sup> In this case, the nonconvergence is caused by low precision of the representation of real numbers.

Such noise can be eliminated by using more precise real number representation. One such option is using another type defined by IEEE 754 standard, namely 80-bit or even 128-bit floating point number formats. However, neither of these is commonly available on today's hardware, let alone in .NET runtime. If we would decide to use one of these two formats, every operation on such numbers would have to be emulated in software, which would greatly slow down the simulator.

Another option would be using .NET type decimal which is a 128-bit representation of floating point numbers different from the IEEE 128-bit format. Its format is not directly supported on currently used processors, and therefore all operations are implemented in software by bit manipulations. Also, this type is intended mainly for handling currency and has approximate range only  $-7.9 \cdot 10^{28}$  to  $7.9 \cdot 10^{28}$ , which is too-narrow range for circuit simulation.

Instead, in the article mentioned above, Mike Robbins proposes using double-double technique. This technique represents a single value as a unevaluated sum of two double floating point values, each of which having its own significand and exponent. This principle is illustrated in figure 1.10 where number  $\pi$  is represented as a sum of two doubles.<sup>9</sup>

### $\underbrace{3.141592653589793}_{}\underbrace{238462643383279}_{}$

$3.141592653589793 \cdot 10^{0} + 2.38462643383279 \cdot 10^{16}$

Figure 1.10: Decomposition of  $\pi$  using double-double technique

Contrary to the options mentioned above, operations on double-double format are implemented using standard operations on double format, which are supported in today's hardware. This means that much higher speeds can be achieved. Hida et al. created a C++ library, that implements both double-double arithmetic, and it's slightly more complicated version – quad-double arithmetic. More details about the algorithms used can be found in their published paper [17].

Using these enhanced precision types is attractive, because they can solve some convergence issues during simulation, and we would therefore like to use

<sup>&</sup>lt;sup>8</sup>In general, there are many reasons why solution might not converge, several possible techniques and simulator parameters used to overcome nonconvergence are explained in Ron Kielkowski's Inside SPICE [3].

<sup>&</sup>lt;sup>9</sup>One thing worth noting is that an implementation of the double-double format needs to decompose values based on the the binary representation of the real numbers. The QD library by Hida et al. [16] uses values 3.141592653589793116e+00 and 1.224646799147353207e-16 in the source code, possibly to compensate errors from truncating periodic binary representation of the mantissa.

them in our library. However, use of these precision types could lead to significant slowdown of the simulation, because multiple primitive operations on doubles are done for each operation on the double-double and quad-double types. This could unnecessarily slow down simulations of circuits which do not require the precision provided by these types. We would therefore like to make these enhanced precision types optional, and otherwise use the standard double precision type. Because our implementation will allow using any of the double, double-double and quad-double types, we would like to compare the simulator performance – i.e. speed and accuracy – when using each of these types to get the basic idea when use of these types is appropriate.

#### 1.5 Goals

- 1. Implement SPICE-like simulation library

- (a) Target .NET Standard for maximum portability

- (b) Support performing time-domain simulation of the circuit, and allow changing parameters of circuit devices between individual timesteps.

- (c) Support following set of devices

- i. Ideal resistor

- ii. Ideal voltage source

- iii. Ideal current source

- iv. Ideal inductor

- v. Ideal capacitor

- vi. SPICE diode

- vii. SPICE BJT transistor

- (d) Allow new types of circuit analyses and circuit devices to be added to the simulator without modifying the library's source code.

- (e) Implement SPICE netlist parser to allow importing circuits and macromodels from standard SPICE netlist files.

- (f) Allow users of the library to choose between double, double-double, and quad-double precision types and compare the library's performance with respect to speed and accuracy for each listed precision type.

- 2. Use the simulation library to implement SPICE-like console application for .NET Core, which would accept implemented subset of SPICE netlist syntax.

## 2. The SPICE Netlist Syntax

This chapter presents the netlist syntax, which we plan to support in the NextGen SPICE library for importing circuits and in the standalone console application. The syntax presented here is a subset of that supported by SPICE3, and can be further restricted to that of SPICE2.

## 2.1 General Syntax

The SPICE netlist syntax is case insensitive. The netlist file consists of individual statements, which are separated by line breaks. If a statement is to span multiple lines, every subsequent line must be prefixed with a + symbol. Following code fragments are therefore equivalent.

```

V1 0 1

+ SIN 0 5V 10KHZ

```

V1 0 1 SIN 0 5V 10KHZ

Statements themselves are made up of individual data fields, delimited by blank characters. The meaning of data fields depends on the actual statement and on the position inside the statement. Generally, a data field specifies either a name, or a numeric value, and is then called name field or number field, respectively.

#### 2.1.1 Number Fields

If the statement expects a data field to represent a numeric value, then the (number) field should start with a digit. However, if a decimal number is specified, the leading zeros may be omitted (therefore, .05 is a valid number field having same value as 0.05). It is also possible to specify the scale by either using suffixes like E-9 or one of the scaling factors listed in the following table.

| Factor | Scale      |

|--------|------------|

| Т      | $10^{12}$  |

| G      | $10^{9}$   |

| MEG    | $10^{6}$   |

| K      | $10^{3}$   |

| M      | $10^{-3}$  |

| U      | $10^{-6}$  |

| N      | $10^{-9}$  |

| Р      | $10^{-12}$ |

| F      | $10^{-15}$ |

Any additional characters that follow the number and scale factor are ignored, so fields 10000, 10E+3V, 10K, 10KV, 10KVOLTS and 10KHz all represent the same value. This is convenient, because the ignored part may be used to specify units and thus improve readability of the netlist file.

#### 2.1.2 Name Fields

On the other hand, if a data field is to represent a name, an arbitrary string of alphanumeric characters can be used.

#### 2.1.3 Comments

The input file can also contain comments, which are completely ignored by the parser. Comments begin with an asterisk \* symbol, and end by a line break. Comments can be used to further improve readability of the netlist file.

V1 0 in 5 \* a 5V voltage source between the ground and 'in' node

#### 2.2 Data Statements

Data statements are used to describe the actual circuit and can be further divided into *device statements* and *model statements*. Device statements specify individual circuit devices and their connections to circuit nodes and generally have the following form:

<device name> <terminal connections> <device arguments>

The concrete SPICE device type is determined by the first letter of the device name, and from the device type, the number of terminal connections and arguments is derived. Like SPICE3, we will not pose any restrictions on the length of the device name.<sup>1</sup>

After the name follows a list of nodes to which the device connects. Nodes are identified by arbitrary alphanumeric strings.<sup>2</sup> The ground node is identified as 0. After the terminal connections follows a device dependent argument list.

Model statements are used to specify parameters for more complex semiconductor devices, so that multiple devices can have the same parameters without their extensive repetition throughout the netlist file. Model statement has the following structure:

.MODEL <model name> <model type> (<model parameter list>)

Each device can accept only model types corresponding to that particular device type. Each model type has a set of parameters, which are set in the model parameter list, each having its default value. When defining new model, only non-default values need to be specified by a list of key value pairs in the form <name>=<value>. The model name is then supplied as an argument to semiconductor devices such as a diode.

Following sections describe formats of several SPICE device statements. Values beginning with N are for node connections, values enclosed in square brackets are optional. Also, when applicable, the available model types and names of their parameters are listed.

<sup>&</sup>lt;sup>1</sup>in SPICE2, the length was limited to seven characters only

<sup>&</sup>lt;sup>2</sup>In SPICE2, nodes are identified by integers, one consequence of this is that 00 and 0 are equivalent in SPICE2, but not in SPICE3.

#### 2.2.1 Resistor

R<name> N+ N- <resistance>

A simple ideal resistor device. The order of N+ and N- nodes has no effect on the circuit behavior.

Examples:

R1 1 2 50HM R2 2 3 1K

#### 2.2.2 Capacitor

C<name> N+ N- <capacitance> [IC=<initial voltage>]

An ideal capacitor device, initial voltage can be specified to set specific condition on the beginning of the simulation. If initial condition is not present, capacitor is modeled as an open circuit in the first DC operating point calculation.

Examples:

C1 1 2 1F C2 2 3 1N IC=1M

#### 2.2.3 Inductor

L<name> N+ N- <capacitance> [IC=<initial current>]

An ideal inductor device, initial current can be specified to set specific condition on the beginning of the simulation. If initial condition is not present, capacitor is modeled as an ideal short circuit in the first DC operating point calculation.

Examples:

L1 1 2 1F L2 2 3 1N IC=1M

#### 2.2.4 Input sources

$$N+$$

$N N N N N-$

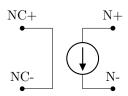

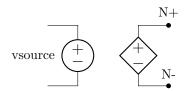

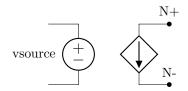

V<name> N+ N- <source function> I<name> N+ N- <source function>

NextGen SPICE supports complex specification of input source behaviors. Possible source functions are listed below.

#### DC Source

[DC] <voltage>

A source that has constant value, the DC identifier can be omitted. Examples:

V1 1 0 5V I2 1 2 DC 10KV

#### Sinusoidal Source

SIN <vo> <va> <freq> [ [ [<ph>]]]

| Parameter       | Meaning            |

|-----------------|--------------------|

| <00>            | Value offset       |

| <va></va>       | Value amplitude    |

| <fr></fr>       | Waveform frequency |

|                 | Delay time         |

|                 | Damping factor     |

| <phase></phase> | Phase offset       |

A sinusoidal source with amplitude damping. Value of the source function is given by

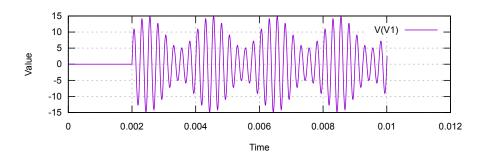

$$f(t) = \begin{cases} <\texttt{vo>} & \text{if } t < \texttt{td>} \\ <\texttt{vo>} + <\texttt{va>} & e^{-(t-<\texttt{td>})\cdot<\texttt{th>}} \\ & \cdot \sin\left(2\pi \cdot \left(<\texttt{fr>} \cdot (t-<\texttt{td>}) + <\texttt{ph>}\right)\right) \end{cases} \text{ if } t \geq <\texttt{td>} \end{cases}$$

Example:

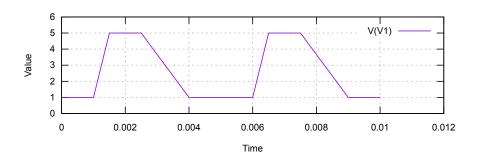

V1 1 0 SIN 1 5 2KHZ 1MS 0.5K

#### **Exponential Source**

EXP <v1> <v2> [<td1> <tau1> [<td2> <tau2>]]

| Parameter     | Meaning                   |

|---------------|---------------------------|

| <v1></v1>     | Initial value             |

| <v2></v2>     | Pulse value               |

| <td1></td1>   | Delay before first edge   |

| <tau1></tau1> | First edge time constant  |

| <td2></td2>   | Delay before second edge  |

| <tau2></tau2> | Second edge time constant |

A pulsing source with exponential rising and falling edges. Values of the source are given by:

$$f(t) = \begin{cases} \langle \mathtt{v1} \rangle & \text{if } t < \mathtt{td1} \rangle \\ \\ \langle \mathtt{v1} \rangle + \left( \langle \mathtt{v1} \rangle - \langle \mathtt{v2} \rangle \left[ 1 - e^{\frac{-(t - \langle \mathtt{td1} \rangle)}{\langle \mathtt{tau1} \rangle}} \right] \right) & \text{if } \langle \mathtt{td1} \rangle \ge t > \langle \mathtt{td2} \rangle \\ \\ + \left( \langle \mathtt{v1} \rangle - \langle \mathtt{v2} \rangle \left[ 1 - e^{\frac{-(t - \langle \mathtt{td1} \rangle)}{\langle \mathtt{tau1} \rangle}} \right] \right) & \text{if } t \ge \langle \mathtt{td2} \rangle \\ \\ + \left( \langle \mathtt{v2} \rangle - \langle \mathtt{v1} \rangle \left[ 1 - e^{\frac{-(t - \langle \mathtt{td2} \rangle)}{\langle \mathtt{tau2} \rangle}} \right] \right) & \text{if } t \ge \langle \mathtt{td2} \rangle \end{cases}$$

Example:

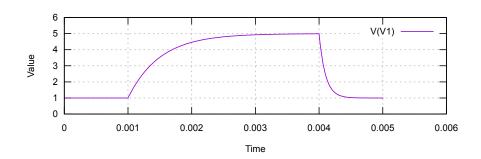

V1 1 0 EXP 1 5 1MS 0.5M 4MS 0.1M

#### **Pulse Source**

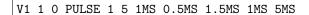

PULSE  $\langle v1 \rangle$   $\langle v2 \rangle$   $\langle td \rangle$   $\langle tf \rangle$   $\langle ton \rangle$   $\langle period \rangle$

| Parameter         | Meaning                               |

|-------------------|---------------------------------------|

| <v1></v1>         | Initial value                         |

| <v2></v2>         | Pulse value                           |

|                   | Delay before rising edge of the pulse |

|                   | Time of the rising edge of the pulse  |

| <tf></tf>         | Time of the falling edge of the pulse |

| <ton></ton>       | Duration of the pulse                 |

| <period></period> | Period of the source                  |

A source that sends individual pulses. Example:

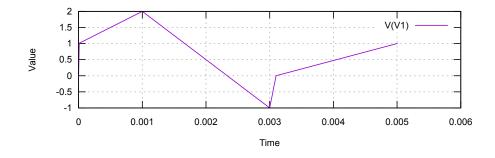

#### Piecewise Linear Source

An arbitrary piece-wise linear source. The argument list consists of pairs of timepoints and source values. The intermediate values are determined using linear interpolation.

Example:

#### **AM Source**

AM <amp> <dc> <fm> <fc> [ [<ph>]]

| Parameter     | Meaning                                   |

|---------------|-------------------------------------------|

| <amp></amp>   | Peak amplitude of the unmodulated signal. |

| <dc></dc>     | DC offset                                 |

| <fm></fm>     | Modulation frequency                      |

| <fc></fc>     | Carrier frequency                         |

|               | Delay before the signal                   |

| <ph>&lt;</ph> | Phase offset                              |

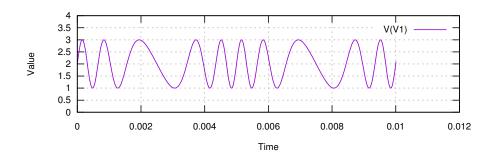

A source with amplitude modulated signal. Value at any given timepoint is given by

$$f(t) = \texttt{} \frac{\cdot \left(\texttt{} + \sin\left(2\pi \cdot \texttt{} \cdot (t - \texttt{>})\right) + \texttt{}\right)}{\cdot \sin\left(2\pi \cdot \texttt{} \cdot (t - \texttt{>}) + \texttt{}\right)}.$$

Example:

#### V1 1 0 AM 5 2 0.5KHZ 4KHZ 2MS

#### **SFFM Source**

| Parameter   | Meaning                   |

|-------------|---------------------------|

| <dc></dc>   | DC offset of the signal   |

| <amp></amp> | Amplitude of the carrier. |

| <fc></fc>   | Carrier frequency         |

| <m></m>     | Modulation index          |

| <fm></fm>   | Modulation frequency      |

A source with frequency modulated signal. Value at any given timepoint is given by

$$f(t) = \texttt{} + \texttt{} \cdot \sin{(2\pi \cdot \texttt{} \cdot (t - \texttt{>}) + m \cdot \sin{(2\pi \cdot \texttt{} \cdot (t - \texttt{>}))})}.$$

Example:

#### V1 1 0 SFFM 2 1 1KHZ 3 0.2KHZ

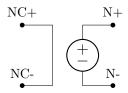

#### 2.2.5 Controlled Sources

SPICE supports linear dependent sources, both current and voltage controlled. In case of voltage controlled source, an additional pair of terminals is specified, and value of the source is linearly dependent on the voltage between those control terminals. In case of current controlled sources, a name of a voltage source is supplied and the value of the source depends linearly on the current flowing through said device.<sup>3</sup> The coefficient of linear dependence, called *gain* is supplied as the last parameter.

#### Voltage Controlled Voltage Source

E<name> N+ N- NC+ NC- <gain>

Example:

E1 1 2 3 4 100

#### Voltage Controlled Current Source

G<name> N+ N- NC+ NC- <gain>

Example:

G1 1 2 3 4 100

#### Current Controlled Voltage Source

$<sup>^3</sup>$ The reason that only voltage source can be used is that the current flowing through the voltage source is directly accessible through a circuit variable in the equation system. Also, because earlier versions of SPICE could output only currents flowing through voltage sources, it became a standard practice to use 0V voltage sources as amperemeters.

#### Example:

VMETER 1 2 0 H1 2 3 VMETER

#### **Current Controlled Current Source**

F<name> N+ N- <vsource> <gain>

#### Example:

VMETER 1 2 0 F1 2 3 VMETER

#### 2.2.6 Diode

D<name> N+ N- <model name>

A semiconductor diode device. Physical parameters of diode are set using a .MODEL statement with D model type. Following table lists supported model parameters for the diode model. The parameters in gray are parsed, but do not affect the simulation in the current implementation.

| Parameter name | Description                             | Default v          | alue                 |

|----------------|-----------------------------------------|--------------------|----------------------|

| IS             | Saturation current                      | $1 \cdot 10^{-14}$ | A                    |

| RS             | Ohmic resistance                        | 0                  |                      |

| N              | Emission coefficient                    | 1                  |                      |

| TT             | Transit-time current                    | 0                  | S                    |

| CJO            | Zero-bias junction capacitance          | 0                  | F                    |

| VJ             | Junction potential                      | 1                  | V                    |

| M              | Grading coefficient                     | 0.5                |                      |

| EG             | Activation energy                       | 1.11               | eV                   |

| XTI            | Saturation-current temperature exponent | 3                  |                      |

| KF             | Flicker noise coefficient               | 0                  |                      |

| AF             | Flicker noise exponent                  | 1                  |                      |

| FC             | Coefficient for forward-bias            | 0.5                |                      |

|                | depletion capacitance formula           | 0.0                |                      |

| BV             | Reverse breakdown voltage               | $\infty$           | V                    |

| IBV            | Current at breakdown voltage            | $1 \cdot 10^{-3}$  | A                    |

| TNOM           | Parameter measurement temperature       | 27                 | $^{\circ}\mathrm{C}$ |

#### Example:

D1 1 2 1N4148 .MODEL 1N4148 D(IS=2.52N RS=.568 N=1.752 CJO=4P M=.4 TT=20N VJ=20 BV=75)

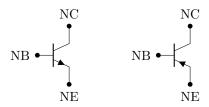

## 2.2.7 BJT Transistor

Q<name> NC NB NE <model name>

A semiconductor BJT transistor device. Physical parameters of BJT are set using a .MODEL statement, as well as the polarity of the transistor. There are two model types for BJT transistor: NPN and PNP. Both model types accept the same parameters, which are listed in the following table. The parameters in gray are parsed, but do not affect the simulation in the current implementation.

| Parameter | Description                                   |            | 1             |

|-----------|-----------------------------------------------|------------|---------------|

| name      |                                               |            | Default value |

| IS        | Transport saturation current                  | 1.0e16     | A             |

| BF        | Ideal maximum forward beta                    | 100        |               |

| NF        | Forward current emission coefficient          | 1.0        |               |

| VAF       | Forward Early voltage                         | $\infty$   | V             |

| IKF       | Corner for forward beta high current roll-off | $\infty$   | A             |

| ISE       | B-E leakage saturation current                | 0          | A             |

| NE        | B-E leakage emission coefficient              | 1.5        |               |

| BR        | Ideal maximum reverse beta                    | 1          |               |

| NR        | Reverse current emission coefficient          | 1          |               |

| VAR       | Reverse Early voltage                         | $\infty$   | V             |

| IKR       | Corner for reverse beta high current roll-off | $\infty$   | A             |

| ISC       | Leakage saturation current                    | 0          | A             |

| NC        | Leakage emission coefficient                  | 2          |               |

| RB        | Zero bias base resistance                     | 0          |               |

| IRB       | Current where base resistance                 | $\infty$ A | Λ             |

| IND       | falls halfway to its min value                |            | A             |

| RBM       | Minimum base resistance at high currents      | RB         |               |

| RE        | Emitter resistance                            | 0          |               |

| RC        | Collector resistance                          | 0          |               |

| CJE       | B-E zero-bias depletion capacitance           | 0          | F             |

| VJE       | B-E built-in potential                        | 0.75       | V             |

| MJE       | B-E junction exponential factor               | 0.33       |               |

| TF        | Ideal forward transit time                    | 0          | S             |

| XTF       | Coefficient for bias dependence of TF         | 0          |               |

| VTF  | Voltage describing VBC dependence of TF       | $\infty$ | V                    |

|------|-----------------------------------------------|----------|----------------------|

| ITF  | High-current parameter for effect on TF       | 0        | Α                    |

| PTF  | Excess phase at freq=1.0/(TF*2PI) Hz          | 0        | deg                  |

| CJC  | B-C zero-bias depletion capacitance           | 0        | F                    |

| VJC  | B-C built-in potential                        | 0.75     | V                    |

| MJC  | B-C junction exponential factor               | 0.33     |                      |

| XCJC | Fraction of B-C depletion capacitance         | 1        |                      |

| ACJC | connected to internal base node               | Т        |                      |

| TR   | Ideal reverse transit time                    | 0        | S                    |

| CJS  | Zero-bias collector-substrate capacitance     | 0        | F                    |

| VJS  | Substrate junction built-in potential         | 0.75     | V                    |

| MJS  | Substrate junction exponential factor         | 0        |                      |

| XTB  | Forward and reverse beta temperature exponent | 0        |                      |

| EG   | Energy gap for temperature effect on IS       | 1.11     | eV                   |

| XTI  | Temperature exponent for effect on IS         | 3        |                      |

| KF   | Flicker-noise coefficient                     | 0        |                      |

| AF   | Flicker-noise exponent                        | 1        |                      |

| FC   | Coefficient for forward-bias                  | 0.5      |                      |

|      | depletion capacitance formula                 | 0.5      |                      |

| TNOM | Parameter measurement temperature             | 27       | $^{\circ}\mathrm{C}$ |

#### Examples:

```

Q1 1 2 3 QMOD1

.MODEL QMOD1 PNP(IS=1P)

Q2 4 5 6 QNL

.MODEL QNL NPN(BF=80 RB=100 TF=0.3NS TR=6NS CJE=3PF CJC=2PF VAF=50V)

```

#### 2.2.8 Subcircuits

Subcircuits are SPICE netlist term for device macromodels mentioned back in the introduction chapter. Following syntax is used.

```

.SUBCKT <subcircuit name> <terminal nodes> <subcircuit description> .ENDS

```

Description of the subcircuit has to be enclosed between .SUBCKT and .ENDS statement. The .SUBCKT statement states the name of the subcircuit and lists names of terminal nodes, which will be then used to connect the subcircuit to the outer circuit. There must be at lesst one terminal node and none of them can be 0 (ground node).

The actual description of the subcircuit can contain only data statements – device statements, .MODEL statements, and other .SUBCKT statements. Also, it is customary to place a comment line describing the meaning of the terminal nodes (like in figure 1.4).

Any names defined inside a subcircuit are strictly local to the subcircuit. Therefore, models and subcircuits defined inside the subcircuit cannot be used after the .ENDS statement.

Subcircuit can then be used as an individual device by following syntax:

```

X<name> <terminal nodes> <subcircuit name>

```

where <subcircuit name> is the name supplied in the corresponding .SUBCKT statement, and <terminal nodes> names appropriate number of nodes to which the subcircuit should connect.

Example:

```

.SUBCKT ACAMPLIFIER 2 1 3

R1 1 4 2K

R2 4 0 500

C1 2 4 10n

Q1 3 4 5 2N2222

Rc 1 3 2K

Re 5 0 1e3

.MODEL 2N2222 PNP(BF=50 IS=1E-13 VBF=50)

.ENDS

XOPAMP 1 2 3 ACAMPLIFIER

```

#### 2.2.9 Summary of the Device Statements

| Device             | Syntax                                                                     |

|--------------------|----------------------------------------------------------------------------|

| Resistor           | R <name> N+ N- <resistance></resistance></name>                            |

| Capacitor          | C <name> N+ N- <capacitance> [IC=<voltage>]</voltage></capacitance></name> |

| Inductor           | L <name> N+ N- <inductance> [IC=<current>]</current></inductance></name>   |

| Voltage source     | V <name> N+ N- <source function=""/></name>                                |

| Current source     | I <name> N+ N- <source function=""/></name>                                |

| Voltage controlled | E <name> N+ N- NC+ NC- <gain></gain></name>                                |

| voltage source     | Extrames N. N. NO. NO (8a11)                                               |

| Voltage controlled | G <name> N+ N- NC+ NC- <gain></gain></name>                                |

| current source     | dynames M. M. Mo. Mo. Zgriis                                               |

| Current controlled | H <name> N+ N- <voltage source=""> <gain></gain></voltage></name>          |

| voltage source     | IT THAIRES IN IN TOTAL BOULGES TRAINS                                      |

| Current controlled | F <name> N+ N- <voltage source=""> <gain></gain></voltage></name>          |

| current source     | 1 Mamo, W. Wolldage Boulee, Salli,                                         |

| Diode              | D <name> N+ N- <model name=""></model></name>                              |

| BJT transistor     | Q <name> NC NB NE <model name=""></model></name>                           |

#### 2.3 Control Statements

Control statements are used for performing circuit simulations.

#### 2.3.1 .OP Statement

.OP

The .OP statement is used for requesting DC operating point analysis, which means calculating the values of node voltages and branch currents corresponding to a stable state of the circuit. This statements does not have any arguments.

#### 2.3.2 .TRAN Statement

.TRAN <timestep> <stop time> [<start time>]

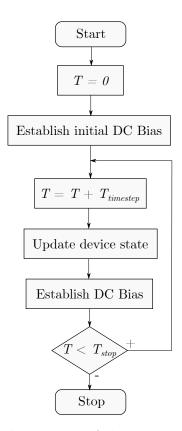

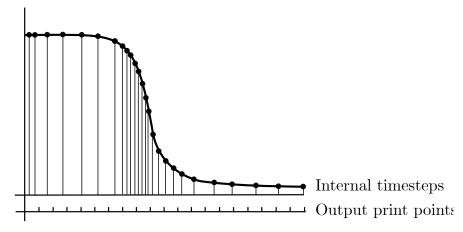

This statement is used for requesting the transient analysis — time-domain simulation of the circuit — for specified duration with given timestep. For each timepoint, an operating point is established, and time-dependent behavior of devices such as capacitor and inductor is modelled using numerical integration methods. If we are not interested only in data after certain timepoint, we can use the third optional parameter to instruct the simulator to not print simulation results until a certain timepoint.

## 2.4 Output Statements

Output statements can be used to select which data should be printed in the simulator's output. If no output statement is provided, NextGen SPICE will print all available data. Currently, the only supported statement is the .PRINT statement.

.PRINT <analysis type> <list of requested data>

Analysis type is either OP or TRAN, indicating from which analysis type the data are requested. Following table summarizes possible data specifiers.

| Specifier                           | Description                                                       |

|-------------------------------------|-------------------------------------------------------------------|

| V( <node>)</node>                   | Voltage of the node <node></node>                                 |

| V( <node1>,<node2>)</node2></node1> | Voltage between nodes <node1> and <node2></node2></node1>         |

| V( <device>)</device>               | Voltage across the <device> device<sup>4</sup></device>           |

| I( <device>)</device>               | Current flowing through the <device> device<sup>4</sup>.</device> |

<sup>&</sup>lt;sup>4</sup>Only devices having exactly two terminals are allowed.

#### 2.5 Netlist File Structure

The structure of the netlist can be almost arbitrary, the only restrictions are that the first line, called *title line*, should contain a brief description of the netlist contents (and is not interpreted as a statement), and that the last statement is a .END statement. There are no restrictions on the relative order of statements in the netlist. For example, semiconductor device models can be used in device statements even before they are defined by their respective .MODEL statement. However, even though any order is possible, netlist files are commonly structured in the following manner:

- Title

- Device statements

- .MODEL statements

- Control statements

- Output statements

- .END statement

## 2.6 Circuit Topology Constraints

There are some restrictions on how the circuit devices can be connected to nodes. These restrictions help ensuring that the equation system rising from the simulated circuit always has unique solution. The rules are the following:

- The circuit may not contain cycles consisting of voltage defined devices (e.g. voltage sources and inductors)

- The circuit may not contain cutsets consisting of current defined devices (e.g. current sources and capacitors)

- In a circuit, there must exist a path from each node to the ground node

- In a subcircuit, there must exist a path between each pair of terminals that does not contain the ground node

## 3. Implementation Analysis

Just like other modern day circuit simulators, our library is also heavily influenced by the original Berkeley SPICE. We have decided to reflect this fact on the name our library and call it NextGen SPICE, and we will use this name in the remainder of this thesis.

This chapter analyses various possibilities of NextGen SPICE simulator implementation. The reader should be acquainted with the necessary theory of circuit simulation. Ron Kielkowski's Inside SPICE [3] is an excellent source of details about the workings of SPICE-like simulators. Necessary mathematical theory is nicely summarized in the documentation of QUCS simulator [18], which we will cite frequently in the next chapters. Another great source is the Ph.D. theses of Laurence W. Nagel (Author of SPICE2) [19]. The last two sources are freely available and we include them in the attached CD for convenience.

## 3.1 Initial Organisation of the library

One of the goals of this thesis is implementation of configurable and extensible circuit simulation library. One of the requirements is that new types of circuit analyses as well as new circuit devices can be added without modification of the core library's source code (goal 1d). Before we start with the actual analysis, we will briefly describe how the original SPICE program operates.

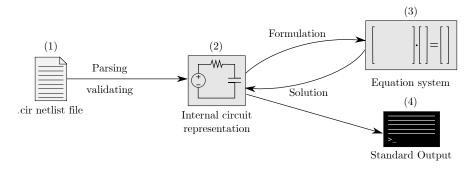

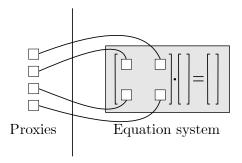

#### 3.1.1 Overview of SPICE Simulator Workflow

The top level view on the SPICE simulator is summarized in the figure 3.1. The user specifies the circuit to be simulated inside a SPICE netlist file (1). This file is parsed by SPICE, which constructs an internal representation of the circuit (2) and validates the circuit topology according to the rules described in section 2.6. If the circuit is correctly formed, SPICE performs the simulations specified in the netlist file. This consists of mapping the devices into coefficients in an equation system characterizing the circuit (3). This equation system is then solved to obtain the result of the analysis, which is then stored in the circuit representation. The user-specified characteristics of the circuit devices are then printed to the output (4).

Figure 3.1: SPICE operation workflow.

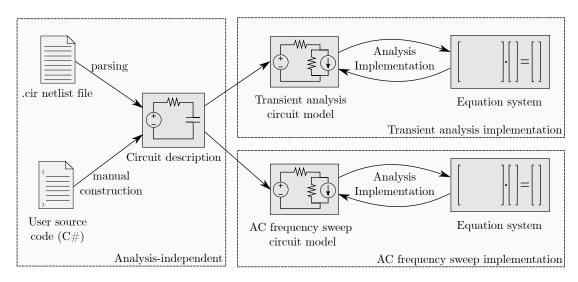

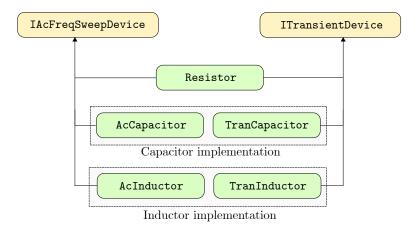

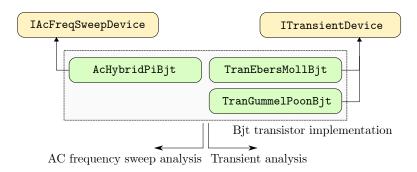

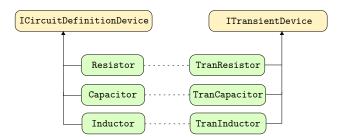

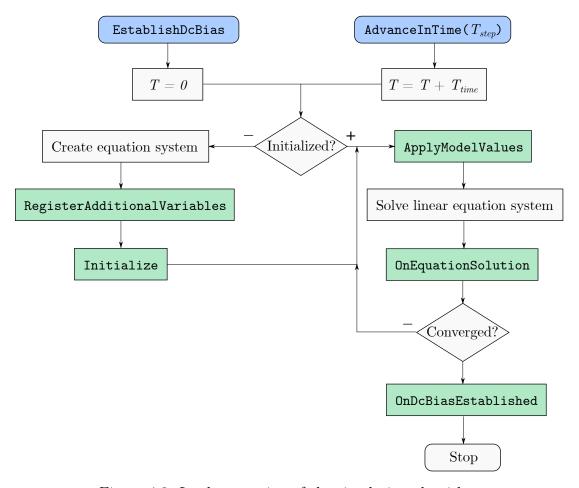

Because different analyses simulate different characteristics of circuit devices, most devices contribute to the equation system coefficients differently in each circuit analysis. To provide a concrete example, the following two paragraphs briefly describe two distinct kinds of circuit analyses: transient analysis (implementation of which is part of this thesis), and AC frequency sweep analysis (which we would like to implement in future versions), and their specific way of simulating capacitors and inductors.

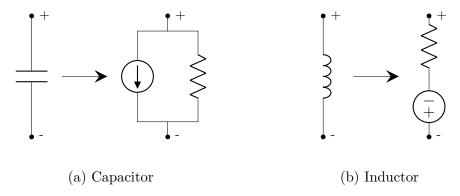

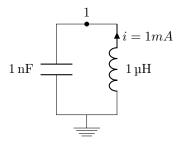

In transient analysis, the circuit's behavior is simulated over time. The first step of this analysis is calculating the initial DC bias of the circuit, which is the technical term for calculating the node voltages and currents flowing through the circuit branches. During this step, capacitors are modeled as ideal open circuits and inductors as ideal short circuit. In subsequent timepoint calculations, capacitor and inductor devices are modeled by equivalent subcircuits consisting of a voltage or current source and a resistor. Values of voltage, current and resistance in these equivalent subcircuits are recomputed each timepoint to reflect energy storing behavior of these devices.

AC frequency sweep analysis simulates how the circuit behaves when a signal of certain frequency is applied to the it. As opposed to transient analysis, which iterates over time, AC frequency sweep iterates over frequency of the applied signal. It also starts by calculating the DC bias of the circuit, but after that, nonlinear characteristics of circuit devices are not modeled. Instead the behavior of each device around the established DC operating point is considered to be linear, which simplifies the analysis. Contrary to the transient analysis which models energy storing behavior of capacitors and inductors, AC frequency sweep models their reactance, which depends on the signal frequency and device's capacitance and inductance, respectively. Additional difference between transient and AC frequency sweep analyses is that in AC frequency sweep analysis, the equation system that characterizes the circuit contains complex numbers as coefficients, whereas in the transient analysis, only real numbers are needed.<sup>2</sup>

## 3.1.2 Separating Circuit Analyses

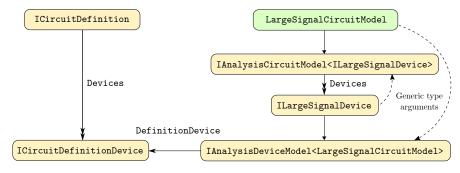

Suppose we used same workflow as in the figure 3.1 and implemented the transient analysis via instance methods on the circuit representation. When we would want to implement AC frequency sweep analysis to the simulator, we would have to modify the circuit representation and add new methods and data fields, which contradicts our goal of extensibility (goal 1d). In order to leave the transient analysis implementation intact, we would have to create a brand new circuit representation that would implement the operations needed by the AC frequency sweep analysis.

<sup>&</sup>lt;sup>1</sup>Consequence of modeling capacitor as open circuit and inductor as short circuit is that the simulation starts from a stable (quiescent) state of the circuit, SPICE simulators allow user to specify custom initial conditions: voltage across the capacitor and current flowing through the inductor, and thereby starting the simulation from an unstable state.

<sup>&</sup>lt;sup>2</sup>Additional details about how capacitors and inductors are modeled can be found in QUCS technical papers. For trasient analysis, see sections 6.3.1 and 6.3.2 for capacitor and inductor, respectively; and for AC analysis see sections 9.3 for capacitor and 9.4 for inductor. More detailed description of individual SPICE circuit analyses can be found in chapter 2 of Inside SPICE p. 37–41