## MASTER THESIS

# David Ligr

# Parallel Evaluation of Numerical Models for Algorithmic Trading

Department of Software Engineering

Supervisor of the master thesis: RNDr. Martin Kruliš, Ph.D.

Study programme: Computer Science

Study branch: Software Systems

| I declare that I carried out this mast<br>cited sources, literature and other pro- | er thesis independently, and only with the ofessional sources.                                                                    |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| No. 121/2000 Sb., the Copyright Act,<br>Charles University has the right to c      | as amended, in particular the fact that the onclude a license agreement on the use of to Section 60 subsection 1 of the Copyright |

| In date                                                                            | signature of the author                                                                                                           |

Title: Parallel Evaluation of Numerical Models for Algorithmic Trading

Author: David Ligr

Department: Department of Software Engineering

Supervisor: RNDr. Martin Kruliš, Ph.D., Department of Software Engineering

Abstract: This thesis will address the problem of the parallel evaluation of algorithmic trading models based on multiple kernel support vector regression. Various approaches to parallelization of the evaluation of these models will be proposed and their suitability for highly parallel architectures, namely the Intel Xeon Phi coprocessor, will be analysed considering specifics of this coprocessor and also specifics of its programming. Based on this analysis a prototype will be implemented, and its performance will be compared to a serial and multi-core baseline pursuant to executed experiments.

Keywords: parallelization, GPU, Xeon Phi, algorithmic trading, support vector machines

First of all, I would like to express my gratitude to my supervisor RNDr. Martin Kruliš, PhD. for his comments, remarks and support. Further, I am very grateful to all my friends, who read this work and helped me with corrections.

Last but not least, I would like to thank my family for supporting me during the studies, especially my wife Eva for her patience and encouragement.

# Contents

| 1 | Intr          | oduct                | ion 4                                             |  |  |  |

|---|---------------|----------------------|---------------------------------------------------|--|--|--|

|   | 1.1           | Perfor               | mance and Parallelism                             |  |  |  |

|   | 1.2           | Objec                | tives                                             |  |  |  |

| 2 | Ope           | enCL                 | 7                                                 |  |  |  |

|   | 2.1           | Struct               | sure of OpenCL                                    |  |  |  |

|   |               | 2.1.1                | Language Specification                            |  |  |  |

|   |               | 2.1.2                | Platform Layer and Runtime API                    |  |  |  |

|   | 2.2           | Platfo               | rm Model                                          |  |  |  |

|   | 2.3           | 3 Execution Model    |                                                   |  |  |  |

|   |               | 2.3.1                | Kernel Execution on a Compute Device              |  |  |  |

|   |               | 2.3.2                | Host Program                                      |  |  |  |

|   | 2.4           | Memo                 | ry Model                                          |  |  |  |

|   |               | 2.4.1                | Accessing Shared Memory Simultaneously            |  |  |  |

|   | 2.5           | Best I               | Practices                                         |  |  |  |

|   |               | 2.5.1                | Work Decomposition                                |  |  |  |

|   |               | 2.5.2                | Synchronization                                   |  |  |  |

|   |               | 2.5.3                | Reusing of Data                                   |  |  |  |

|   |               | 2.5.4                | Data Layout                                       |  |  |  |

| 3 | Inte          | Intel Xeon Phi       |                                                   |  |  |  |

|   | 3.1           | Archit               | secture                                           |  |  |  |

|   |               | 3.1.1                | Vector Processing Units                           |  |  |  |

|   |               | 3.1.2                | Memory Architecture                               |  |  |  |

|   | 3.2           | 2 OpenCL Programming |                                                   |  |  |  |

|   |               | 3.2.1                | Kernel Execution on Intel Xeon Phi Coprocessor 24 |  |  |  |

|   |               | 3.2.2                | Local Memory                                      |  |  |  |

|   |               | 3.2.3                | Comparison with GPUs                              |  |  |  |

| 4 | $\mathbf{AT}$ | Model 28             |                                                   |  |  |  |

|   | 4.1           | Techn                | ical Analysis                                     |  |  |  |

|   |               | 4.1.1                | Technical Indicators                              |  |  |  |

|   |               | 4.1.2                | Univariate Analysis                               |  |  |  |

|   |               | 4.1.3                | Multivariate Analysis                             |  |  |  |

|   |               | 4.1.4                | Supervised Learning Algorithms                    |  |  |  |

|   | 4.2           | Suppo                | ort Vector Machine                                |  |  |  |

|   |               | 4.2.1                | Theory of SVMs                                    |  |  |  |

|    |               | 4.2.2   | Kernel Function                              | 35         |  |  |  |  |

|----|---------------|---------|----------------------------------------------|------------|--|--|--|--|

|    |               | 4.2.3   | SVM in Regression                            | 37         |  |  |  |  |

|    | 4.3           | Existin | ng AT Model                                  | 37         |  |  |  |  |

| 5  | Imp           | lemen   | tation                                       | <b>4</b> 0 |  |  |  |  |

|    | 5.1           | Analys  | sis                                          | 40         |  |  |  |  |

|    |               | 5.1.1   | Preprocessing                                | 41         |  |  |  |  |

|    |               | 5.1.2   | Approaches to Parallelization                | 41         |  |  |  |  |

|    | 5.2           | Archit  | secture Specific Parallelization             | 44         |  |  |  |  |

|    |               | 5.2.1   | Multi-Core Parallelization                   | 44         |  |  |  |  |

|    | 5.3           | Many-   | Core Parallelization                         | 45         |  |  |  |  |

|    |               | 5.3.1   | Evaluating Kernel Method In Parallel         | 46         |  |  |  |  |

|    |               | 5.3.2   | Evaluating Multiple Blocks Simultaneously    | 48         |  |  |  |  |

|    |               | 5.3.3   | Parallel Aggregation                         | 49         |  |  |  |  |

|    |               | 5.3.4   | Preprocessing                                | 51         |  |  |  |  |

|    |               | 5.3.5   | Data Layout                                  | 51         |  |  |  |  |

|    |               | 5.3.6   | Command-Queues and Kernel Synchronization    | 52         |  |  |  |  |

|    | 5.4           | Progra  | amming Language, Data Formats, and Libraries | 52         |  |  |  |  |

|    |               | 5.4.1   | Data Types                                   | 53         |  |  |  |  |

|    |               | 5.4.2   | Parallel Programming in .NET                 | 53         |  |  |  |  |

|    |               | 5.4.3   | OpenCL Host Bindings in .NET                 | 54         |  |  |  |  |

|    | 5.5           | Imple   | mentation for GPUs                           | 55         |  |  |  |  |

| 6  | Exp           | erime   | ntal Results                                 | 57         |  |  |  |  |

|    | 6.1           |         |                                              | 57         |  |  |  |  |

|    |               | 6.1.1   | Execution Time                               | 58         |  |  |  |  |

|    |               | 6.1.2   | Correctness of Measured Times                | 58         |  |  |  |  |

|    |               | 6.1.3   | Hardware Specification                       | 59         |  |  |  |  |

|    |               | 6.1.4   | Test Data                                    | 60         |  |  |  |  |

|    |               | 6.1.5   | Testing Configuration                        | 60         |  |  |  |  |

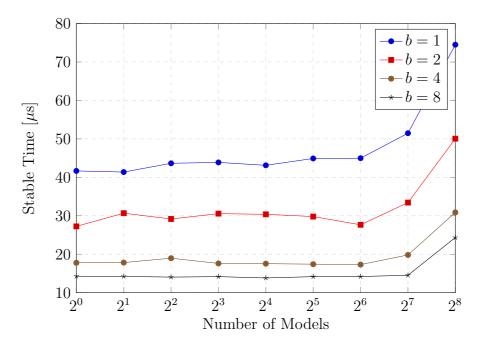

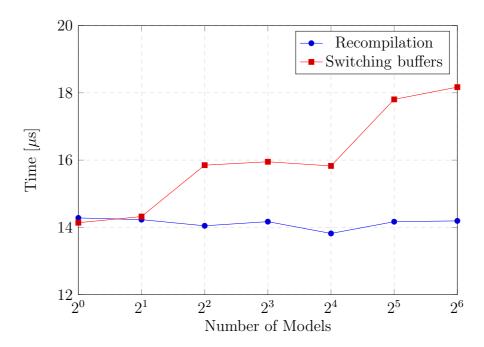

|    | 6.2           | Perfor  | mance                                        | 60         |  |  |  |  |

|    |               | 6.2.1   | Measured Times                               | 61         |  |  |  |  |

|    |               | 6.2.2   | Scalability                                  | 63         |  |  |  |  |

|    | 6.3           | Cost    | of Modifications                             | 65         |  |  |  |  |

| 7  | Conclusion 67 |         |                                              |            |  |  |  |  |

| -  | 7.1           |         | e Work                                       | 67         |  |  |  |  |

| Bi | iblio         | graphy  |                                              | 69         |  |  |  |  |

|    |               |         |                                              |            |  |  |  |  |

| Li | st of         | Figure  | es                                           | 72         |  |  |  |  |

| List of Tables        | 73 |

|-----------------------|----|

| List of Abbreviations | 74 |

| Attachments           | 75 |

# 1. Introduction

Trading on stock markets mainly consists of selling and buying trading instruments, such as shares, obligations, or derivatives. All these operations are performed pursuant to many aspects, which can be grouped into two disjoint sets: rational aspects and irrational aspects. The examples of rational aspects include a progression of a price of the given trading instrument, progressions of prices of trading instruments related to the given trading instrument, or a due date of the corresponding obligation. The irrational aspects are for example intuition and feelings of the trader.

Up to the 1950s, all activities concerning buying and selling instruments were carried out by traders. Consequently, decisions could have been influenced by irrational aspects as well as rational aspects. Thanks to that, an unexpected drop of price of owned trading instrument might have led to a lossy decision, which was based on fear and nervosity of the trader rather than indicias coming from an analysis of rational aspects. This was one of the most important reasons why Harry Markowitz came in his dissertation thesis [1] with the idea of applying mathematical concepts to stock markets. This idea combined with computers development led to emergence of algorithmic trading (AT). From that time on, trading operations can be assisted by algorithmic trading or fully executed by it.

In algorithmic trading, mathematical models are transformed into computer algorithms. This allows processing of enormous amount of data in a short period of time and therefore it is possible to quickly react to occurring situations. This is one of the most important reasons why algorithmic trading was utilized in up to 63% of all trades done on the US stock markets in 2011 (this number was published in The Economist [2]). However, it is important to note that even though a trader leaves part of their activities to a computer program, certain decisions can still be made by the trader themselves. These activities typically include an execution of trading instructions (algorithmic execution), while the trader still makes a decision about their issuing.

High-frequency trading (HFT) is the primary form of algorithmic trading on financial markets. High-frequency trading represents so-called algorithmic decision-making. In algorithmic decision-making, a computer is also responsible for issuing trade requests in contrast to algorithmic execution, in which a trader is responsible for this issuing. The main characteristics of high-frequency trading include a fast reaction to events occurring on the market and also hundreds to thousands of orders and messages issued to the market per seconds.

## 1.1 Performance and Parallelism

Companies dealing with algorithmic trading utilize so-called co-location, i.e. they place their servers right into the buildings where the stock markets are situated. A close physical proximity leads to shorter communication paths and to lower communication latency.

Another technique being used to improve performance is utilization of more powerful hardware. Until the beginning of the 21st century, the power of contemporary processors could have been easily improved by the frequency increase. In that time, the frequency of processors reached a limit of about 3 GHz, beyond which processors consume too much energy and consequently produce too much heat. In order to solve this problem, processor developers had to adopt a new approach to improve the performance. Therefore they shifted their focus on optimizing hardware architecture and on creating multi-core and many-core architectures.

Even though general-purpose processors include a wide range of functional units to respond to any computational demand, only some of these units are utilized in common computation. The problem concerning idle units is that they are still powered, even though far less than utilized ones. Besides general-purpose processors, there are specialized processors, such as graphic cards or parallel accelerators, which are optimized for processing of large blocks of data in parallel. Thanks to this, these processors do not contain such a wide range of functional units, and therefore have better performance per watt than general-purpose processors.

Graphic cards and parallel processors are representatives of so-called many-core architectures. Such architectures allow executing 10-1000 of threads in parallel, and eventually deliver an enormous amount of raw performance. In order to utilize this performance, we have to adopt new ways of designing algorithms, developing applications, and thinking about problems. Applications that utilize that performance are rated both by criteria applicable to single-threaded applications (such as their efficiency or the time complexity) and by scalability with more threads or cores.

Although parallelism can improve throughput in orders of magnitude, it introduces many new issues (such as thread management or synchronization) that do not concern us in single-threaded applications. All these problems have to be addressed properly, in order to create flawless and efficient applications.

In contrast to the fact that parallelism can improve overall computation throughput, it might deteriorate computation latency. Thanks to this, parallelism is not suitable for simple computations, as in these computations latency interests us more than overall throughput.

## 1.2 Objectives

In this work we will analyze an existing model for high-frequency trading, which predicts future prices of a trading instrument on the basis of multiple indicators, from the perspective of parallel programming. Based on this analysis, we will implement a prototype, which will efficiently utilize a highly parallel architecture, namely Intel Many Integrated Core (MIC) Architecture, and compare the performance of this prototype implementation to a baseline serial and multi-core CPU algorithm.

In Chapter 2, we will describe OpenCL, which allows us to implement our prototype for the Intel MIC Architecture. Chapter 3 will explain specifics of programming for Intel Xeon Phi, which is the first product based on that architecture. The description of the existing algorithmic trading model and its analysis will follow in Chapter 4. Chapter 5 will be dedicated to the explanation of implementation techniques and details. The empirical results of our research and their interpretation will be presented in Chapter 6.

# 2. OpenCL

OpenCL (Open Computing Language) [4] is open, royalty-free standard for cross-platform, parallel programming of diverse processors found in personal computers, servers etc. A primary benefit of OpenCL is substantial improvement of speed and responsiveness of a wide spectrum of applications from various market categories, e.g., gaming, scientific and medical software, etc. A second benefit is cross-vendor software compatibility.

When we wish to utilize OpenCL we have to perform even several tasks permitting this utilization. For now, we will describe these tasks at the highest possible level of abstraction. A more elaborate description of the terms stated in the rest of this paragraph is the subject of next subchapters that briefly introduce models constituting OpenCL. The first step to using OpenCL is querying the platform, i.e. vendor specific OpenCL implementation, from the host program for available devices and selecting a subset of them to be utilized for a computation. After that, a context containing selected devices is created. The created context is after here utilized for creating a command-queue, through which the host program orchestrates a single device within the context, a kernel, i.e. a function to be executed on the devices contained in the context, and memory objects, which hold input or output data of a kernel invocation. When the command-queue, the kernel, and memory objects are created, the host program submits commands to transfer memory objects onto the device, execute the kernel, and transfer yielded data back onto the host to the command-queue.

## 2.1 Structure of OpenCL

The OpenCL development framework comprises 2 parts:

- Language specification

- Platform layer and runtime API

## 2.1.1 Language Specification

The language specification describes the syntax and programming interface for writing kernels, i.e. functions to be executed on supported devices in parallel.

```

1 --kernel void add_matrices(

2    constant float* const matrix_a,

3    constant float* const matrix_b,

4    global float* const matrix_c)

5    {

6        int r = get_global_id(0);

7        int c = get_global_id(1);

8        int n = get_global_size(0);

9        int index = n*r +c;

10        matrix_c[index] = matrix_a[index] + matrix_b[index];

11    }

```

Listing 2.1: Source code of kernel performing addition of matrices.

The kernels are written in the OpenCL C [5] programming language. OpenCL C is based on the ISO C99 specification with added extensions and restrictions. Additions include vector data types, vector operations, address space qualifiers and a *kernel* function qualifier, which denotes a kernel function. The source code of a simple kernel function, which encompasses the kernel qualifier and the address space qualifiers, is depicted in Listing 2.1. Restrictions contain the absence of support for function pointers, bit fields, recursion, and variable-length arrays.

## 2.1.2 Platform Layer and Runtime API

The platform layer API permits the programmer query the system for the existence of OpenCL supported devices. Using this API, a programmer could also control which subset of available devices will constitute the context in any OpenCL application.

The OpenCL runtime API provides the functions to manage objects such as command-queues, memory objects and kernel objects, as well as functionality for executing kernels on one or more devices defined in the context.

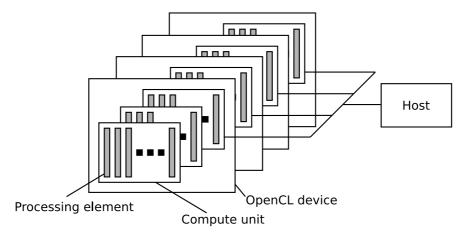

#### 2.2 Platform Model

The OpenCL platform model defines a high-level abstraction of any heterogeneous platform used with OpenCL. An OpenCL platform always incorporates a single host which has a general-purpose CPU and one or more OpenCL devices. A schema of such a platform is depicted in Figure 2.1<sup>1</sup>.

An OpenCL device can be a CPU, a GPU, or any other accelerator device that

<sup>&</sup>lt;sup>1</sup>Figures presented in this chapter are based on figures contained in *OpenCL Programming Guide* [6].

Figure 2.1: A schema of the OpenCL platform model.

is supported by OpenCL. The device is where kernels are executed. Therefore, an OpenCL device is often referred to as a compute device.

An OpenCL device consists of at least one compute unit, which itself is composed of one or more processing elements. These elements execute computational work that is to be executed on a relevant compute device. For instance, in case a compute device is a multi-core CPU, then each of its cores corresponds to a compute unit and slots in SIMD registers correspond roughly to processing elements.

## 2.3 Execution Model

An OpenCL application consists of two main execution units: host program and kernels. As we mentioned earlier, kernels are basic unit of executable code that runs on one or more OpenCL devices. The host program executes on the host system and uses the runtime API to interact with objects defined within OpenCL.

## 2.3.1 Kernel Execution on a Compute Device

Before we will describe, how kernels execute on compute devices, we have to introduce data parallelism inasmuch as OpenCL utilizes this kind of parallelism when executing these kernels. Data parallelism refers to scenarios in which the same function executes on different elements of a some collection in parallel. Note that this programming model requires elements in this collection to be independent of each other.

Since data parallelism is about executing a given function on multiple elements of some collection a work associated with execution of that function on a single element conforms to the base unit of work. In OpenCL, this unit of work is called a *work-item*. The total number of work-items, which execute on processing elements, to be executed is defined by the size of an index space, which is called a *global index space*. This index space is defined when a kernel is queued for execution by the host program.

Work-items are aggregated into work-groups. All work-items in the same work-group are executed together on the processing elements of a single compute device. The reason for execution on a single compute unit is to allow work-items to share resources and synchronize their execution. It is particularly important to realize that the work-items in different work-groups cannot be synchronized, and therefore, accessing the same data by work-items belonging to different work-groups may lead to a malfunction.

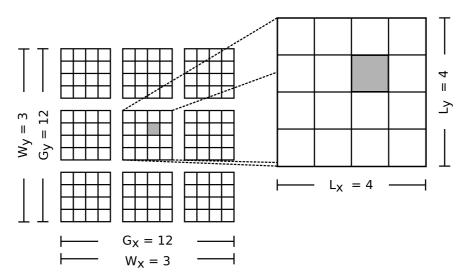

#### Index spaces

As stated, the size of the global index space defines the total number of workitems that require execution. In other words, a work-item is executed for each point in the global index space and, therefore, coordinates of a point uniquely identifies both this point and the associated work-item. These coordinates are commonly referred to as a *global ID* of a work-item.

Since a work-group encompasses related work-items, it provides a more coarse-grained decomposition of the global index space. OpenCL requires all the work-groups to have the same size, i.e. the number of contained elements that divides the global size without a residue. Besides this, a work-group is, just like each work-item, assigned a unique group ID.

Figure 2.2: An example of how the global IDs, the local IDs, and work-group IDs are related. The shaded block has the global ID of  $(g_x, g_y) = (6,5)$  and the local ID of  $(l_x, l_y) = (2,1)$ .

Besides the global ID, a work-item is assigned a local ID, which is unique

within the work-group containing this work-item. Hence, a work-item can be uniquely identified by its global ID or by a combination of its local ID and its work-group ID. The relation between the local ID and the global ID of a work-item is illustrated in Figure 2.2.

In fact, OpenCL supports up to 3-dimensional index spaces. The supported dimensions correspond to dimensions of entities, e.g., vectors, images, 3D models, whose processing provides opportunities to utilizing data parallelism.

When work-items of a multidimensional index space should be executed by processing elements a mapping of them to these processing elements, i.e. a mapping from a multidimensional space into a one-dimensional space has to be utilized. OpenCL uses the function  $f(x, y, z) = x + y \cdot size_x + z \cdot size_x \cdot size_y$ , where x corresponds to index in the first dimension and  $size_x$  corresponds to the size of the original index space in the first dimension and so on, for this mapping.

## 2.3.2 Host Program

The host program is responsible for setting up and managing the execution of kernels on OpenCL devices.

In order to dispatch a kernel for execution, the host program has to do following:

- 1. select an OpenCL platform encompassing devices to be employed in the computation

- 2. initialize a context using a subset of devices from the selected platform

- 3. initialize command-queues, program objects, kernels, and memory objects associated with the context

Command-queues, program objects, kernels, and memory objects are essential for any OpenCL application, and therefore, they will be described thoroughly in the rest of this chapter.

#### Program Object and Kernel

An OpenCL program comprises kernels, data constants and other functions that are non-invokable by the host. A program object encapsulates the program source code or a binary file containing the program executable along with the list of devices for which the executable is built.

When a program object is successfully created, it may be built for one or more devices that are encapsulated by the program object. The reason, why the program objects are built only at runtime, is based on the fact that an OpenCL programmer writes an application for an end user and does not know on which CPUs, GPUs, or other parallel devices the end user may run the application on. In the other words, a programmer only knows that the target devices conform the OpenCL specification. Therefore, only after defining devices the program is to be executed on, the program object can be appropriately compiled for these devices. In addition, the knowledge of target devices enables the OpenCL compiler to optimize the code in a way suitable for these devices.

```

var platform = ComputePlatform.Platforms[0];

var context = new ComputeContext(

ComputeDeviceTypes.Gpu,

new ComputeContextPropertyList(platform),

null,

IntPtr.Zero);

var program = new ComputeProgram(context, clSourceCode);

program.Build(null, null, null, IntPtr.Zero);

var kernel = program.CreateKernel("addKernel");

```

Listing 2.2: Initialization of a general OpenCL application.

A kernel object, i.e. an object encapsulating a kernel function, is created after the executable has been successfully built in a program object.

All steps required for a creation of a kernel object are stated in Listing 2.2, which contains a snippet of the host source code.

#### Command-Queues

OpenCL does not support direct communication of the host with devices, instead of this the host communicates with devices by submitting commands to command-queues. A command-queue is created by the host and attached to exactly one OpenCL device.

The order commands submitted to a single command-queue execute is determined by the type of the command-queue. There are 2 types of command-queues:

- In-order command-queue: Commands are launched and completed in the same order in which they placed onto the command-queue. In other words, this type guarantees that a command begins only after the preceding commands are finished.

- Out-of-order command-queue: Commands are launched in the order that is based on synchronization constraints placed on these commands.

As we have explained above, commands in an in-order command-queue can begin only after all previously enqueued commands are completed. This can decrease performance because of underutilized compute units. Utilization of compute units can be significantly improved by using an out-of-order command-queue, since a command can be launched regardless of whether previously enqueued commands are completed or not. So when a compute unit finishes its work, it can immediately fetch a new command and start its execution. This is called automatic load balancing and it is a well know technique used in the design of parallel algorithms driven by command queues [3].

Regrettably, support of the out-of-order mode is optional, and therefore not implemented on certain platforms. On these platforms, multiple command-queues can be employed to utilize compute units more efficiently. Commands in different command-queues may run concurrently, and only the host can synchronize execution of these commands.

OpenCL supplies three types of commands:

- **Kernel execution**: a command that invokes a kernel for execution on a device, it also specifies the global index space over which the kernel is to be executed

- Memory transfer: a set of commands that transfer data between the host and the memory objects, copy the memory objects, or manage memory mappings

- Synchronization: a set of commands that constrain order of command execution or synchronize the host execution with a device execution

Memory transfer commands and synchronization commands may be blocking and non-blocking. The OpenCL function call for a non-blocking command returns immediately after the command is enqueued regardless of whether the command is completed or not. On the other hand, the OpenCL function call for a blocking counterpart returns once the command is completed.

The kernel execution commands and the memory transfer commands are used in each OpenCL application. A basic usage of these commands is depicted in Listing 2.3. On the lines 1-2, a command-queue associated with the first device within the context is initialized. The lines 3-5 contain initialization of memory objects. These memory objects are set to the arguments of the kernel, on the following 3 lines. The lines 9-10 include enqueuing of writing of input data, which are obtained elsewhere, to the input memory objects. This implies that buffers bufferA and bufferB represent input memory objects while the last buffer represents an output memory object. On the line 11, the kernel is submitted to the command-queue for execution. On the last line, reading of data yielded by the kernel execution is enqueued.

```

var commandQueue = new ComputeCommandQueue(context,

context.Devices[0], ...);

var bufferA = new ComputeBuffer<float > (...);

var bufferB = new ComputeBuffer<float > (...);

var bufferC = new ComputeBuffer<float > (...);

kernel.SetMemoryArgument(0, bufferA);

kernel.SetMemoryArgument(1, bufferB);

kernel.SetMemoryArgument(2, bufferC);

commandQueue.WriteToBuffer(matrixA, bufferA, ...);

commandQueue.WriteToBuffer(matrixB, bufferB, ...);

commandQueue.Execute(kernel, ...);

commandQueue.ReadFromBuffer(bufferC, ref matrixC, ...);

```

Listing 2.3: Source code of an application submitting a kernel for execution.

Synchronization commands are used to constrain the order of execution of multiple commands or of the host and a device. Emphasize that the order of execution of commands issued to the same in-order command-queue is fixed by the order in which commands were enqueued, and thus, it is meaningless to constrain it further using synchronization commands.

The first command that can be used to synchronize execution of multiple commands is *clEnqueueBarrier*. This command enqueues a synchronization point ensuring that all commands enqueued to the same command-queue before have finished execution before following commands begin execution.

As stated, using clEnqueueBarrier we are able to synchronize execution of neither commands issued to different command-queues nor of the host and a command. Therefore, OpenCL provides a clFinish command, which blocks the host until all previously enqueued OpenCL commands in an appropriate command-queue have finished. Therefore, future commands will not begin execution inasmuch as they will be neither submitted to command-queues until the previous ones have finished. The fact that this command is blocking makes it unsuitable when only execution of multiple commands need to be synchronized, since it also blocks a calling thread on the host despite it is not required.

To synchronize commands in different command-queues defined in the same context while not stalling a calling thread on the host we have to use so-called event-objects. An event object is generated when a command is submitted to a command-queue and communicates the status of the associated command. A clEnqueue WaitForEvents command, which accepts a collection of event-object as one of its parameters, ensures that all commands to which passed event-objects are associated have finished before any future commands queued to the command-queue begin execution. This means that the clEnqueueWaitForEvents command, in contrast to the clEnqueueBarrier, may be used to synchronize commands in

multiple command-queues and moreover allows to specify commands that have to complete before future commands can begin execution. State that OpenCL provides even a blocking counterpart of this command, namely *clWaitForEvents*, that may be used to synchronize the host execution with execution of commands forming a subset of previously submitted commands.

The last way how to synchronize execution of multiple commands in different command-queues defined in the same context is also based on utilizing event-objects. In this case, a collection of event-objects is passed to a command to be synchronized as one of its parameters. This command then can begin its execution only when each event-object in the passed collection communicates that the associated command has finished. This means that this way of synchronization provide much more fine-grained control than utilizing the clEnqueueWait-ForEvents command, since this way constrains the execution order of a particular command and not of all future commands.

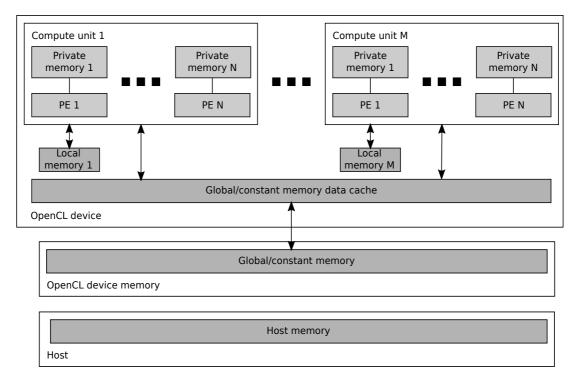

## 2.4 Memory Model

The OpenCL memory model defines 2 types of the memory objects: buffer objects and image objects, which are not usable for the purposes of this work, and therefore, will not be further described. A buffer object stores a one-dimensional collection of elements of a scalar data type, vector data type, or a user-defined structure. Elements of a buffer object can by accessed using a pointer by a kernel executing on a device.

The OpenCL memory model defines, besides memory objects, 5 distinct memory regions:

- Host memory: This memory region resides in the host RAM, and therefore, is visible only to the host. As in the case of the host program, OpenCL only defines how the host memory interacts with the OpenCL objects.

- Global memory: This memory region is accessible by the host, and permits reads and writes to all work-items in all work-groups. Reads and writes to the global memory may be cached depending on the capabilities of the device. This memory region and the host memory is in case a device is GPU, Xeon Phi or another coprocessor independent of each other. Due to this, data stored on the host needs to be transferred to the global memory or vice versa.

- Constant memory: This memory is a region of global memory that remains constant during the execution of a kernel. Thanks to this, this memory is better cached than the global memory.

- Local memory: This memory region is associated with a work-group and is accessible only by work-items in this work-group. The time needed to access variables in this memory region is guaranteed not to be greater than the time needed to access variables in global memory. Hence, a common optimization technique utilized in data-intensive applications is based on copying hot data to this memory region.

- **Private memory**: This memory belongs to a work-item, and therefore, is used to store its local variables.

Figure 2.3: The mapping of the OpenCL memory model to the OpenCL platform model.

When we described the global memory, we stated that data has to be transferred between this memory and the host memory, unless the host and a device share memory and caches. Transferring of data can be performed in one of the two ways: by explicit **copying** of data or by **mapping** and **unmapping** regions of memory objects.

The mapping allows the host to map a region of a memory object into its address space. Once the region from the memory object has been mapped, the host can access this region directly. The host has to unmap the region after use to propagate changes back to the devices.

In case of the device connected to the host by a bus, transferring data between the host memory and the global memory has to be done via this bus. Consequently, such transferring is usually slower in order of units than accessing data in memory. This is determined by the fact that currently buses do not provide such throughput as memories. Hence, utilizing OpenCL is primarily convenient for applications in which the computation time is at least roughly equal to the time the host or the device wait for data being transferred.

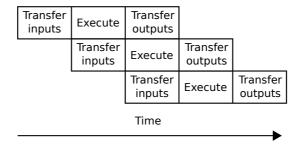

Figure 2.4: An example of transfers and executions pipelining.

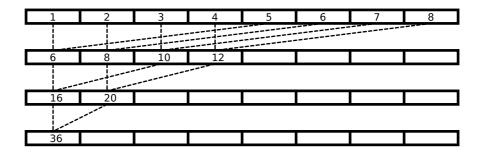

However, some OpenCL devices support pipelining, i.e. simultaneous data transfers in both direction and computations, as illustrated in Figure 2.4. Therefore, the slowdown introduced by transferring data may be reduced by partitioning the input data into several parts to be processed independently. Such partitioning yields the following consequences:

- the time the device is waiting data is reduced since only a part of the original data is transferred

- the other parts of the original data may be transferred to the device while it executes on the preceding parts.

## 2.4.1 Accessing Shared Memory Simultaneously

When concurrent execution is introduced, a special attention has to be paid to the consistency of shared memory to avoid potential race conditions.

The first issue that must be addressed is concurrent manipulating the same memory location. For this purposes, OpenCL implements a few atomic operations, which only apply to integers and longs except for a single function for floats. These operations guarantee that an operation on a given memory location is thread-safe, which means no other work-item can access to that location while the atomic operation is executing.

Another issue to be addressed is the visibility of changes made by a single work-item to other work-items. This is essential especially in case when multiple work-items cooperate in computation. OpenCL guarantees that changes made by a work-item are visible to other work-items in the same work-group only at work-group synchronization point. For example, a work-group barrier forces all stores

defined before it to complete before any work-items in the work-group proceed past it. On the other hand, OpenCL does not provide any way of enforcing consistency of shared memory between work-items belonging to different workgroups.

## 2.5 Best Practices

To conclude this chapter we will present several programming rules and recommendations that are based on the previously stated facts.

## 2.5.1 Work Decomposition

The peak performance of an arbitrary device is possible to achieve only when all its computation resources are utilized. Therefore, a computation has to be partitioned to at least as many independent parts as the number of processing elements of a device this computation runs on, since otherwise some processing elements of the device will be idle. Therefore, devices equipped with up 1000 of processing elements, e.g., GPUs or other highly-parallel devices, necessitate partitioning of computations to be executed on them to an enormous number of independent parts.

## 2.5.2 Synchronization

Synchronization forces some processing elements to wait until a specific event occurs, e.g., all work-items in a work-group reach a synchronization point, or a command is communicated as finished, and therefore, it is expensive. Hence, synchronization should be avoided as much as possible.

## 2.5.3 Reusing of Data

Data should be kept on a device as long as possible. This means that programs that run multiple kernels on the same data should favor leaving the data on the device between kernel invocations, rather than reading intermediate results to the host and then sending them back to the device for subsequent calculations. Reusing of data thus improves the performance, since it reduces the number of transfers, which are fairly costly.

## 2.5.4 Data Layout

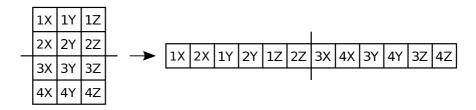

Every time when a computation executes on a collection, which will be further referred to as a source collection, of structures comprising multiple fields, a serious attention should be paid to the selection of the data layouts in which the source collection will be arranged. Because this choice may have a large impact on overall computation performance. Although OpenCL supports an array of a structure we will arrange the source collection into an array of a simple data type, which we will be denoted as a destination array. There are 3 different data layouts that are being used to arrange such a collection into a destination array.

The first data layout is referred to as the Array-of-Structures (AoS). This data layout arranges fields of a single item of the source collection to consecutive indices of the destination array. However, using this data layout once multiple threads access the same field of consecutive items results in using of scatter and gather instructions, since these fields occupy indices with the stride sized the number of the fields of the structure. On this account, such memory access is termed as a strided memory access. Due to the hardware capabilities, scatter and gather instructions are typically less efficient than simple vector load and store instructions.

Another layout is called Structure-of-Arrays (SoA). In this case, consecutive indices of the destination array are occupied by the same field of consecutive items. Such access corresponds to a so-called coalesced memory access. Hence, using this data layout does not require usage of scatter and gather instructions in case when consecutive threads execute on consecutive elements of the source. On the other hand, this data layout suffers from poor spatial locality.

The last layout is referred to as Array-of-Structures-of-Arrays (AoSoA). This layout arranges items to an array of structures of small arrays. So, this layout provides a simple vector loads and stores, while does not suffer from poor spatial locality. The problem of AoSoA is readability of the code.

# 3. Intel Xeon Phi

Intel Xeon Phi Coprocessor is the brand name for all Intel Many Integrated Core (MIC) Architecture [7], based products. This architecture is targeted for highly parallel, High-Performance Computing workloads.

The Intel Xeon Phi coprocessor is connected to a CPU, which is referred to as a host, through a PCIe bus. This implies that data could be transferred between the host and the coprocessor with a nominal transfer speed 16 GB/s in each direction. This means that data transfers incur some overhead, and therefore, one should reduce data transfers as much as possible.

A single host system can contain multiple Intel Xeon Phi devices, which can communicate with each other through PCIe peer-to-peer interconnect without any intervention from the host.

## 3.1 Architecture

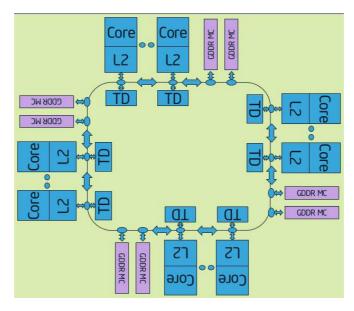

The Intel Xeon Phi coprocessor is composed up to 61 cores, each of which is derived from an Intel Pentium core, augmented by Intel 64 ISA, 4-way simultaneous multithreading, i.e. it can execute instructions from 4 hardware threads simultaneously, and a powerful vector processing unit (VPU). These cores are all connected through on-die wire interconnect, as shown in Figure 3.1.

Figure 3.1: The Intel Xeon Phi processor microarchitecture [8]

The VPU, which is 512-bit wide, is fully pipelined and can execute most instructions with 4-cycle latency and single-cycle throughput. The cores do not

support any previous Intel SIMD extensions like MME, SSE, or AVX. Instead of these, a novel instruction architecture set is implemented to utilize the VPU.

The interconnection is implemented as a bi-directional ring, which carries data and instructions to various agents including cores, memory controllers providing a direct interface to GDDR5 memory on the device, and a globally distributed tag directory. These agents are connected to the ring through ringstops.

Each direction comprises three independent rings, which carry data, addresses, and acknowledgements. The data ring is 64 bytes wide, so it permits transferring data occupying a single cache line, which is also 64 bytes wide, simultaneously. The second ring is used to send read/write commands and memory address, and thus, is denoted as the address ring. The last one transfers flow control and coherence messages.

## 3.1.1 Vector Processing Units

A key hardware feature that dictates the performance of highly-parallel computing on Intel Xeon Phi is the VPU working on 512 bits, i.e. it can execute 16 single-precision or 8 double-precision operations at a time. It can execute most vector operations with four cycle latency and provides the maximal throughput of 1 instruction per cycle, what corresponds to the facts that the VPU is fully pipelined and the core is able to execute instructions from up to 4 hardware threads simultaneously. The VPU can read/write one vector per cycle from/to the vector registers file or data cache simultaneously with one vector operation.

Each VPU has 128 512-bit vector registers divided among the threads, thus, each thread is provided by 32 registers. Besides these vector registers, there are 16 mask registers per thread, which are part of the vector register file.

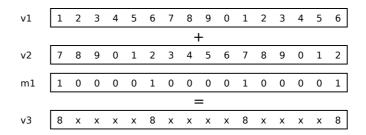

#### Vector Mask Registers

Employing the mask registers one can make the update of the target register element conditional on the bit content of a vector mask register, otherwise, all the destination elements are updated. For this reasons, these registers help to vectorize short conditional branches, as illustrated in Figure 3.2, where elements in m1 register are values to which a predicate evaluates. For this reason, only the v3 register elements corresponding to 1 bit in the m1 register get updated.

#### VPU Pipeline

Each VPU instruction passes through one or more of the following pipelines to completion:

Figure 3.2: An example of conditional updating (x represents an unchanged value).

- **Double-precision pipeline**: Used to execute float64 arithmetic, conversion from float64 to float32, DP-compare instructions.

- Single-precision pipeline: Executes most of the instructions including 64-bit integer loads, float32/int32 arithmetic and logical operations, shuffle/broadcast etc.

- Mask pipeline: Executes mask instructions with one-cycle latencies.

- Store pipeline: Executes the vector store operations.

- Scatter/gather pipeline: Executes the vector register read/writes from sparse memory locations.

It should be noted that interleaving of pipelines and execution of dependent instructions incur time penalties. For this reason, the pipeline can throughput one instruction per cycle only when two independent SP or DP instructions are being executed.

## 3.1.2 Memory Architecture

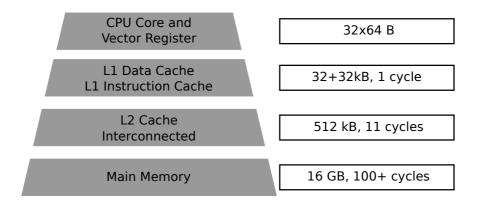

The memory architecture of Intel Xeon Phi coprocessors, which is depicted in Figure 3.3, resembles the memory architecture of CPUs. This means that there is multilevel, hardware managed, coherent cache hierarchy on the top of the memory architecture.

#### Cache

Each core is equipped with a 32 kB L1 instruction cache and 32 kB L1 data cache and a 512 KB L2 cache. The L2 cache is inclusive of the L1 cache, that is, L1 cache lines have to be also included in the L2 cache. Unlike the L1 cache, the L2 cache is unified, so, it caches both data and instructions.

The coherency of data residing in both the L1 cache and the L2 cache among the cores on the ring is maintained by a MESI protocol. In addition to the MESI

Figure 3.3: The memory architecture of the Intel Xeon Phi coprocessor.

protocol [11], the Intel Xeon Phi coprocessor implements a physically distributed tag directory TD along with a TD-based *globally owned*, *locally shared* (GOLS3) protocol. The reason for this is that the supplementing the *MESI* protocol with the *GOLS3* protocol locates the potential performance bottleneck of the *MESI*.

#### Tag Directory

The TD is attached to each core and gets an equal portion of the whole address space. Each physical address is uniquely mapped to TD through a reversible function. A TD entry, which is called a TD tag, contains the address, state and an ID of the owner of the cache line.

On an L2 cache miss, a core references a TD that is uniquely determined by the address, and therefore, it is not necessarily located on the core that generates the miss.

The TD is also responsible for initiating communication with the memory controllers. This communication is initiated on an L2 cache miss when a request is sent to a memory controller from the TD maintaining the requested cache line. Once the memory controller retrieves the requested cache line, it is returned to the requesting core.

State that the L1 cache has lower latency than the L2 cache, which has lower latency than the memory. For this reason, reusing of data residing as close as possible to the core is essential to achieving good performance.

#### **Memory Controller**

The Intel Xeon Phi coprocessor contains up to 8 memory controllers, which are evenly interleaved around the ring. Each of them has 2 channels, which communicate with GDDR5 memory at 5,5 GT/s. This is, the aggregate memory bandwidth equals to 352 GB/s.

The addresses are evenly distributed among the memory controllers to reduce

bottlenecks, and to provide optimal bandwidth. This implies that the consecutive memory locations are distributed among the memory modules and there is no way to place memory close to a core in order to provide optimal memory bandwidth.

#### Applicability of the Intel Xeon Phi Coprocessor

The utilization of the Intel Xeon Phi coprocessor could be beneficial only when the code to be run on the coprocessor has the following characteristics that fit the Intel Xeon Phi architecture:

- The code utilizes all available cores without keeping them idle and even scales with the number of available cores.

- The code is vectorizable and thus utilizes the VPUs efficiently.

- The communication with the host is minimized and overlapped with the computation as much as possible.

## 3.2 OpenCL Programming

As stated in Chapter 2, OpenCL is a framework for cross-platform, parallel programming. Although OpenCL applications may run on various platforms, their performance may vary on these platforms. This is caused by the fact that these platforms may have rather different HW design, and therefore, benefit from different application optimizations. For this reason, the remainder of this chapter will be devoted to the description of optimizations specific for the Intel Xeon Phi coprocessors.

## 3.2.1 Kernel Execution on Intel Xeon Phi Coprocessor

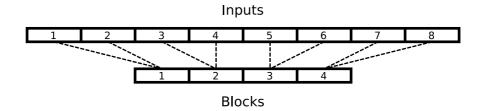

At initialization time, OpenCL creates as many software threads as the Intel Xeon Phi coprocessor contains logical cores, i.e. OpenCL creates 244 software threads in case the coprocessor comprises 61 cores, and pins each of them to one logical core.

After that, when a kernel is submitted for execution, each work-group is assigned to one software thread, which executes all work-items in this work-group. Combining this fact together with the fact that software threads are pinned to logical cores yields that logical cores correspond to compute units.

#### Parallelism among Work-Groups

Since different work-groups are executed by different logical cores they may execute in parallel. This means that utilizing all logical cores at a time necessitates at least as many work-groups as the number of logical cores, otherwise, some of the logical cores will not be utilized. Generally, employing a larger number of work-groups results in more flexibility in scheduling.

Despite the previous recommendation, the execution of work-groups should take at least 100 000 clock cycles in order to keep the proportion of thread switching overhead to actual work reasonably small.

#### Work-Group Level Parallelism

OpenCL on the Intel Xeon Phi coprocessor achieves parallelism also at a work-group level by executing a vectorized kernel, since such a kernel may be partly executed by the VPU. A kernel vectorization, which is done automatically by an implicit vectorization module<sup>1</sup>, consists of unrolling a routine executing a work-group. Such an optimized routine is depicted in Listing 3.1.

```

1 kernel_wrapper (...)

2 #pragma unroll 16

3 for (int local_id = 0; i < WORK_GROUP_SIZE; ++local_id)

4 kernel_body (...)</pre>

```

Listing 3.1: Pseudocode of an optimized routine executing a work-group.

Although the routine executing a work-group comprises up to 3 loops, what corresponds to the maximal supported dimension of index spaces 2.3.1, only the innermost loop that corresponds to the first dimension of the NDRange may be unrolled.

#### Implicit Vectorization

The implicit vectorization module automatically vectorizes the work-group routine in the innermost loop, i.e., the code is unrolled by the vector size, which is 16 regardless of the type of data used in the kernel [10].

Nevertheless, the vectorized kernel is used only if the local size of the first dimension is not less than 16. Otherwise, the OpenCL runtime runs the scalar kernel for each of the work-items. This may introduce a significant performance penalty for work-groups having a small size in the first dimension. Therefore, it is recommended to round up the size in the first dimension to the closest multiple of 16.

<sup>&</sup>lt;sup>1</sup>An implicit vectorization module is a part of the program build process.

#### **Branch Statements**

We distinguish two kinds of control flows, namely uniform and non-uniform control flow. A branch is uniform if it is guaranteed that all work-items within a single work-group will execute the same block of this branch. In the context of the Intel Xeon Phi coprocessor, that is, the branch predicate has to be constant.

```

1 uint mask = get_mask();

2 int res_if = if_block();

3 int res_else = else_block();

4 int res = (res_if & mask) | (res_else & not(mask));

```

Listing 3.2: An example of the masked execution.

In the latter case, a branch is non-uniform. Non-uniform control flows have worse performance than uniform ones since both blocks of the branches have to be executed using masked execution. An example of such execution is contained in Listing 3.2.

## 3.2.2 Local Memory

For the Intel Xeon Phi coprocessors, all OpenCL memory objects are implicitly cached by the hardware. Hence, the commonly used optimization technique based on employing the local memory for caching hot data is beneficial only in case of data scattered in the global memory but compacted in the local memory. In the other case, employing the local memory for caching hot data only introduces unnecessary overhead caused by redundant data copy and management. In other words, utilizing locality of data provides effective memory access on Intel Xeon Phi coprocessors. achieving the peak performance.

## 3.2.3 Comparison with GPUs

In conclusion of this chapter, we will briefly compare OpenCL programming for Intel Xeon Phi coprocessors with OpenCL programming for GPUs. The reason why we opted for GPUs and not for another kind of OpenCL devices is based on the fact that GPUs are suited for data-intensive computations just like Intel Xeon Phi coprocessors and moreover OpenCL programmers are typically familiar with programming for them.

Both Intel Xeon Phi coprocessors and GPUs have many cores and data to execute on kernels have to be transferred to or from them. Therefore, there are aspects that improve performance of OpenCL applications both on these coprocessors. These aspects include:

- Include enough work-groups, which themselves comprise enough work-items, within each NDRange.

- Employ consecutive data accesses or at least good data locality.

- Reduce data transfers from and to the host.

- Overlap data transfers and computations.

- Reduce synchronization on any level and usage of atomic operations.

On the other hand, there are aspects that improve performance of OpenCL applications on the Intel Xeon Phi coprocessors but not on GPUs:

- Avoid small work-groups, i.e. those whose execution takes significantly less than 100 000 clock cycles.

- Do not use local memory for caching data that occupy a block of global memory.

# 4. AT Model

Algorithmic trading uses a well-defined set of rules based on timing, price, quantity, and other mathematical models for identifying favorable opportunities. Such way of identifying favorable opportunities is also known as a *market analysis*.

We distinguish two kinds of the market analysis: a fundamental analysis and a technical analysis.

**Fundamental Analysis** The fundamental analysis uses fundamental factors related to an underlying asset in question to predict its future price. These factors can be grouped into two categories [12]:

- Quantitative: factors capable of being measured or expressed in numerical terms,

- Qualitative: factors related to or based on the quality or character of something, often as opposed to its size or quantity.

In fact, the fundamental analysis is more based on qualitative factors. Beside the fact that these factors are hard to be analysed automatically, they also have slow update frequency as most these factors are linked to quarterly reports. This, combined with the time needed to perform a thorough fundamental analysis, makes this analysis convenient predominantly for trades lasting at least weeks.

From the previous paragraph we conclude that the fundamental analysis is not suitable for HFT, and hence, it will not be described here any further. Instead of this, we will shift our attention to the thorough description of the technical analysis, which, unlike to the fundamental analysis, is convenient for HFT.

## 4.1 Technical Analysis

The technical analysis uses only historical data of trading instruments, such as previous prices and volumes, to predict the future price of the trading instrument. The prediction of the price is also referred to as financial time series forecasting.

Financial time series are inherently noisy and non-stationary, as introduced by Yaser [13]. These facts outline that there is no complete information that could be obtained from the previous behaviour of financial markets to fully capture the dependency between the future price and historical data. Due to this, quite sophisticated approaches have to be used for forecasting of financial time series.

#### 4.1.1 Technical Indicators

To smooth out financial time series, technical indicators, e.g., simple moving average, weighted moving average, or exponential moving average, that are derived from historical data are used. The mentioned indicators are defined as follows, where p denotes all data of a single time series,  $p_t$  denotes the latest, i.e. current value of this series, and  $p_{t-i}$  denotes the i-th newest value.

#### Simple Moving Average

A simple moving average (SMA) is calculated, as its name suggests, as the average value over a defined number of time periods. The defined number of time is often called the order of the model and will be denoted by  $\tau$ .

$$SMA(p,\tau) = \frac{p_t + \ldots + p_{t-\tau}}{\tau}$$

A weighted moving average (WMA) is derived from the SMA by assigning weights to items. Therefore, a WMA can emphasize recent data rather than old data.

#### **Exponential Moving Average**

An exponential moving average (EMA) decreases the weighting of data exponentially with its age. It weights new data with  $1/\tau$  and old data, i.e. the previous EMA, with the remainder  $(\tau - 1)/\tau$ . This implies, the weighting of any item never reaches 0, and therefore the effect of any item is never entirely removed.

$$EMA(p_t, \tau) = \frac{p_t}{\tau} + \frac{\tau - 1}{\tau} EMA(p_{t-1}, \tau)$$

Each model used for financial time series forecasting may utilize one or more these indicators. The utilized indicators determine into which of two disjoint categories is the model classified:

- *Univariate analysis* uses only indicators restricted to the time series being predicted as the input variables,

- Multivariate analysis uses any indicators as the input variable.

## 4.1.2 Univariate Analysis

General, commonly used univariate models are based on AutoRegressive Integrated Moving Average (ARIMA) model. As the name suggests, this model combines an autoregressive model and a moving average model to predict future trends. The autoregressive model specifies that the output variable depends linearly on its own previous values and on a stochastic, i.e. imperfectly predictable, term.

ARIMA is based on the assumption that the time series are linear and stationary<sup>1</sup>. Regrettably, these assumptions are not compliant with the characteristics of financial time series, as stated in [14].

## 4.1.3 Multivariate Analysis

To model non-linear behavior, non-linear time series models, such as a Threshold Autoregressive model [15], an Autoregressive Conditional Heteroscedastic model [16], have been developed. These models and all models that will be introduced in the rest of this chapter perform the multivariate analysis since their inputs are not restricted to indicators derived from the time series being predicted.

However, the non-linear time series models are still limited in the sense of that these models are explicitly defined pursuant to the knowledge of relationships among underlying assets just as the linear time series models are. However, acquirement of the complete knowledge of these relationships is quite difficult, since there are too many non-linear patterns that should be taken into account. Consequently, these models may not be general enough to capture all important relationships.

Both linear and non-linear time series models are representatives of so-called model-base methods of predicting time series. From facts stated in previous paragraphs, it is obvious that these methods are not adequate for problems, whose solution requires knowledge difficult to obtain. Nevertheless, if we have enough historical data we can utilize so-called data-driven models for solving these problems.

The data-driven methods require only a few assumptions about models for problems to be predicted. A data-driven method corresponds to a function that is inferred from a given set of historical data, which are also called training data. State that this function inferring is known as a supervised learning task in the context of machine learning, and thus, the data-driven methods may be also referred to as supervised learning models. Construction of a supervised learning model based on the training data is being performed by an associated supervised learning algorithm.

## 4.1.4 Supervised Learning Algorithms

Supervised learning algorithms take a set of N training data  $T = \{(\vec{x_i}, y_i)\}_{i=1}^N$ , such that  $\vec{x_i} \in \mathbb{R}^D$  is the vector of features, in our case of indicators, of the i-th input and  $y_i \in \mathbb{R}$  is its label, i.e. the desired value. Based on this training set

<sup>&</sup>lt;sup>1</sup>A time series is stationary if its statistical properties are all constant over time.

these algorithms seek a function g that is an element of a set of possible functions  $G \subset \mathbb{R}^D \to \mathbb{R}$ .

There are two basic approaches for choosing the desired function g: Empirical Risk Minimization and Structural risk Minimization. Both these approaches use a loss function  $L: \mathbb{R} \times \mathbb{R} \to \mathbb{R}$  in order to measure how well functions fit the training data. For each training data  $(\vec{x_i}, y_i)$  the loss of predicting  $\bar{y_i} = g(\vec{x_i})$  equals to  $L(y_i, \bar{y_i})$ . This function is utilized by a risk function  $R_T: G \to \mathbb{R}$  that is defined as the expected loss of g.

$$R_T(g) = \frac{1}{|T|} \sum_{(\vec{x_1}, y_1) \in T} L(y_i, g(\vec{x_i}))$$

#### **Empirical Risk Minimization**

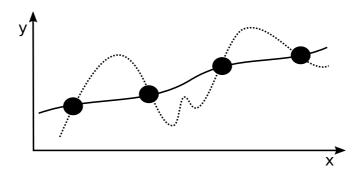

In empirical risk minimization, the associated algorithm seeks a function g that minimizes the risk functions, that is, the supervised learning algorithm prioritizes functions that fit well to the training data but do not take into account their ability of generalization. Note that functions well fitting the training data and having poor generalization are denoted as overfitted. An example of such function is depicted in Figure 4.1, where the dots represent training data, the solid line represents the true function, and the dotted line denotes this unction.

Figure 4.1: An example of overfitting.

#### Structural Risk Minimization

Structural risk minimization [17] seeks a function g that minimizes the upper bound of the generalization error rather than training error. This is done by incorporating a regulation penalty that prefers simple functions over complex ones into optimization.

#### Overfitting

Overfitting generally occurs when a model is excessively complex, such as having too many parameters relative to the number of the training data. Such a model usually has a poor level of generalization, i.e. ability to predict the correct output values for data that were not seen during training, since it describes not only underlying relationships but also random errors and noise. In other words, overfitting occurs when a model begins to memorize the training data rather than generalize from the trend.

## 4.2 Support Vector Machine

A Support Vector Machine (SVM), which was proposed by Vapnik [18], is supervised learning model used for classification and regression analysis.

Although SVMs may be utilized for multiclass classification we will, for sake of simplicity, restrict our description only to SVMs executing binary classification.

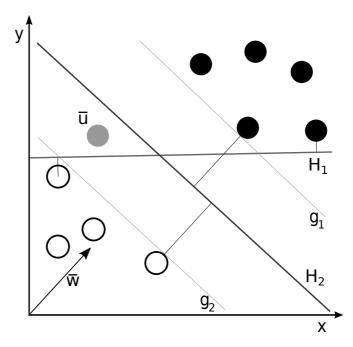

A SVM model of binary classification represents a set of N independent and identically distributed training data  $T = \{(\vec{x_i}, y_i)\}_{i=1}^N \subset \mathbb{R}^D \times \{-1, 1\}$  by a hyperplane separating entries of training data belonging one category, i.e.  $\{\vec{x_i} \mid (\vec{x_i}, y_i) \in T \land y_i = -1\}$  from entries belonging to the other category and withal has the maximal largest distance to the nearest entries of both classes. Such a hyperplane is in Figure 4.2 denoted by  $H_2$  whereas white dots represent entries of the training data belonging to one category, black dots represent entries of the training data belonging to the other category. We will denote a space containing all points distant from the separating hyperplane maximally as the closest points in the training data as a gap. Margins of this gap, which are denoted by  $g_1, g_2$  in that figure, will be referred to as gutters.

Figure 4.2: An instance of SVM.

The separating hyperplane splits the vector space of the training data to two

nonoverlapping parts. These parts are used for classifying new data since they are predicted to belong to one category pursuant to which of these parts includes it.

Maximizing the gap conforms to the fact that the SVMs are based on *structural risk minimization*, unlike most of supervised machine learning models that are based on *empirical risk minimization*. Thanks to this, SVMs are less prone to overfitting and thus provide good generalization with a much bigger probability than traditional models.

# 4.2.1 Theory of SVMs

SVMs carry out binary classification of data  $\vec{u} \in \mathbb{R}^D$  pursuant to a decision rule  $f_T : \mathbb{R}^D \to \{-1,1\}$ . The form of this rule will be expressed in terms of a vector  $\vec{v} \in \mathbb{R}^D$  and a scalar value  $o \in \mathbb{R}$ . The vector  $\vec{v}$  represents a so-called decision vector that has to be perpendicular to the separating hyperplane and the o corresponds to the offset of the separating hyperplane from the origin of the coordinate system in the direction of the vector  $\vec{v}$ . In other words, the offset allows classifying data that are separable by a hyperplane that does not pass the origin inasmuch as it moves the separating hyperplane in a direction of the decision vector. Now, the decision rule should be defined as follows:<sup>2</sup>

$$f_T(\vec{u}) = \begin{cases} 1 & \text{if } \vec{v} \cdot \vec{u} + o \ge 0 \\ -1 & \text{otherwise} \end{cases}$$

(4.1)

In the rest of this subsection, we will describe how  $\vec{v}$  and o are defined based on the training data. The main outcome of this description will be the fact that both  $\vec{v}$  and o may be expressed as a linear combination of the training data, and therefore, even the decision rule may be rewritten as a linear combination of the training data. This also means that the decision rule is easy to calculate using the training data and the scalar product.

Firstly, we have to define additional constraints for each entry of the training data. This constraint has the following form for each  $i \in \{1, ..., N\}$ :

$$y_i(\vec{v} \cdot \vec{x_i} + o) - 1 \ge 0 \tag{4.2}$$

Furthermore, we constrain the left side of the preceding equation to be equal to 0 only if  $\vec{x_i}$  is in the gutters of the gap.

Now, the width of the gap  $w_T$  can be computed using two points  $\vec{x_+}$ ,  $\vec{x_-}$ , each

$<sup>^2\</sup>mathrm{In}$  all equations in this subsection  $\cdot$  represents the scalar product.

lies in a different gutter, as:

$$w = (\vec{x_{+}} - \vec{x_{-}}) \cdot \frac{\vec{v}}{\parallel \vec{v} \parallel} = \frac{(\vec{x_{+}} \cdot \vec{v}) - (\vec{x_{-}} \cdot \vec{v})}{\parallel \vec{v} \parallel} = \frac{(1 - o) - (-1 - o)}{\parallel \vec{v} \parallel} = \frac{2}{\parallel \vec{v} \parallel}$$

(4.3)

In the preceding equation, the second equation utilizes distributivity of the scalar product. The third equation conforms to replacing 1-b for  $\vec{x_+} \cdot \vec{v}$  and -1-b for  $\vec{x_+} \cdot \vec{v}$ , where these operations are compliant with Equation (4.2) and with the previous constraint.

Note that SVMs maximize the width of the gap. However, maximizing  $2/\parallel \vec{v} \parallel$  is quite complicated, so we are going to convert this expression to a mathematically more convenient form.

$$max \frac{2}{\parallel \vec{v} \parallel} \rightsquigarrow max \frac{1}{\parallel \vec{v} \parallel} \rightsquigarrow min \parallel \vec{v} \parallel \rightsquigarrow min \frac{1}{2} \parallel \vec{v} \parallel^2$$

$$(4.4)$$

Maximization of the gap with respect to the constraints defined in Equation (4.2) conforms to solving a so-called quadratic programming problem. For solving this problem we will incorporate the Lagrangian dual function, which yields the following dual formulation:

$$L = \frac{1}{2} \| \vec{v} \|^2 - \sum_{i=1}^{N} \alpha_i (y_i (\vec{v} \cdot \vec{x_i} + o) - 1)$$

(4.5)

where  $\{\alpha_i\}_{i=1}^N$  are Lagrange multipliers.

By computing the first derivation of that expression with respect both to  $\vec{v}$  and o and setting these expressions equal to 0 we can calculate the desired extrema.

$$\frac{\partial L}{\partial \vec{v}} = \vec{v} - \sum_{i=1}^{N} \alpha_i y_i \vec{x_i} = 0 \Rightarrow \vec{v} = \sum_{i=1}^{N} \alpha_i y_i \vec{x_i}$$

$$(4.6)$$

We just proved that the decision vector  $\vec{v}$  is a linear combination of a subset of the training data. This subset, which will be referred to as  $T_S$  in the rest of this chapter, comprises only the training data  $\vec{v}$  associated  $\alpha_i$  that do not equal to 0. Entries included in  $T_S$  are called support vectors.

$$\frac{\partial L}{\partial o} = -\sum_{i=1}^{N} \alpha_i y_i = 0 \Rightarrow \sum_{i=1}^{N} \alpha_i y_i = 0 \tag{4.7}$$

Substitution of  $\vec{v}$  and  $\sum_{i=1}^{N} \alpha_i y_i$  with their expressions stated in 4.6 and 4.7, conduct equation 4.5 to the following form:

$$L = \frac{1}{2} \left( \sum_{i=1}^{N} \alpha_{i} y_{i} \vec{x_{i}} \right) \cdot \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) - \sum_{i=1}^{N} \alpha_{i} y_{i} \left( \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) \cdot \vec{x_{i}} + o \right) - 1 \right)$$

$$L = \frac{1}{2} \left( \sum_{i=1}^{N} \alpha_{i} y_{i} \vec{x_{i}} \right) \cdot \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) - \sum_{i=1}^{N} \alpha_{i} y_{i} \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) \cdot \vec{x_{i}} - \sum_{i=1}^{N} \alpha_{i} y_{i} o + \sum_{i=1}^{N} \alpha_{i}$$

$$L = \frac{1}{2} \left( \sum_{i=1}^{N} \alpha_{i} y_{i} \vec{x_{i}} \right) \cdot \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) - \left( \sum_{i=1}^{N} \alpha_{i} y_{i} \vec{x_{i}} \right) \cdot \left( \sum_{j=1}^{N} \alpha_{j} y_{j} \vec{x_{j}} \right) - o \sum_{i=1}^{N} \alpha_{i} y_{i} + \sum_{i=1}^{N} \alpha_{i}$$

$$L = \sum_{i=1}^{N} \alpha_{i} - \frac{1}{2} \left( \sum_{i=1}^{N} \sum_{j=1}^{N} \alpha_{i} \alpha_{j} y_{i} y_{j} \vec{x_{i}} \cdot \vec{x_{j}} \right).$$

$$(4.8)$$

Solving the preceding equation falls into the theory of mathematical analysis and so it is out of the scope of this work. We reached this point in order to prove that for solving this equation the only operation that is to be performed on the training data is required, namely the scalar product. This fact outlines that solving this equation is computationally manageable since the scalar product is easy to compute.

In addition the fact that the decision vector  $\vec{v}$  is a linear combination of the  $T_S$  subset of the training data, let us rewrite the decision rule (4.1) as follows:

$$f_T(\vec{u}) = \begin{cases} 1 & \text{if } \sum_{\vec{x_i} \in T_S} \alpha_i y_i \vec{x_i} \cdot \vec{u} + o \ge 0\\ 0 & \text{otherwise} \end{cases}$$

(4.9)

This means that even the decision rule depends only on the scalar product, so, we just proved the second part of our statement that was mentioned at the very beginning of this subsection.

Until now, we have tacitly assumed that the training data are linearly separable. However, SVMs are also capable of performing classification of non-linearly separable data. This is done by utilizing a so-called kernel function.

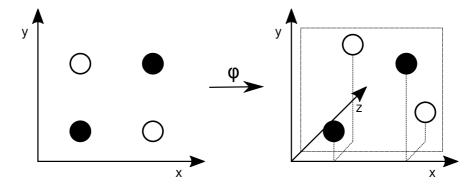

#### 4.2.2 Kernel Function

To separate non-linearly separable input data, these data are mapped to a higher dimensional space, in which they are linearly separable. The mapping is done using a function  $\phi: \mathbb{R}^D \to \mathbb{R}^F$ , where F > D. An example of such mapping is depicted in Figure 4.3, where the outline box depicts the separation hyperplane. The target vector space is called a feature space and image of input vector is known as a feature vector, in the context of SVMs.

Figure 4.3: An example of mapping of non-separable inputs to a feature space.

However, we proved that we do not need to compute the image of a new data in order to classify it but rather compute the scalar product between this image and the images of all support vectors. That is, we seek a function  $K: \mathbb{R}^D \times \mathbb{R}^D \to \mathbb{R}$  conforming  $K(\vec{x_i}, \vec{x_j}) = \phi(\vec{x_i}) \cdot \phi(\vec{x_j})$  for any pair of  $(\vec{x_i}, \vec{x_j}) \in \mathbb{R}^D \times \mathbb{R}^D$ . Such a function is called a kernel function and its utilization transforms the decision rule to the following form:

$$f_T(\vec{u}) = \begin{cases} 1 & \text{if } \sum_{\vec{x_i} \in T_S} \alpha_i y_i K(\vec{x_i}, \vec{u}) + o \ge 0\\ 0 & \text{otherwise} \end{cases}$$

(4.10)

Note that machine learning methods utilizing the kernel functions are called kernel methods. More information about the kernel methods and constraints the kernel methods have to fit are provided in Vapnik [18].

Recently, multiple kernel learning (MKL) methods have been proposed, as stated in Gönen [19]. In this case, we use multiple kernels instead of selecting one particular kernel and its parameters:

$$k_{\eta}(\vec{x_i}, \vec{x_j}) = f_{\eta}(\{k_p(\vec{x_i}, \vec{x_j}) | p \in \{1, \dots, P\}\})$$

(4.11)

where a combination of functions  $f_{\eta}: \mathbb{R}^P \to \mathbb{R}$ , can be any linear or nonlinear function.

There are two main cases of usage of MKL:

- Various kernels correspond to various notations of similarity and instead

of trying to find which works best, a learning method does the picking or

a combination of them for us.

- Different kernels may use inputs from various representations or even various sources. Hence, these inputs have various measures of similarity corresponding to various kernels. Therefore, combining kernels is one possible way of computing the overall similarity.