# Charles University in Prague Faculty of Mathematics and Physics

# MASTER THESIS

Bc. Ján Vojt

# Deep neural networks and their implementation

Department of Theoretical Computer Science and Mathematical Logic

Supervisor of the master thesis: doc. RNDr. Iveta Mrázová CSc.

Study programme: Informatics

Specialization: Software Systems

| I declare that I carried out this master thesis independently, and only with the cited sources, literature and other professional sources.                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I understand that my work relates to the rights and obligations under the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular the fact that the Charles University in Prague has the right to conclude a license agreement on the use of this work as a school work pursuant to Section 60 paragraph 1 of the Copyright Act. |

| In Prague, dated Author's signature                                                                                                                                                                                                                                                                                                           |

Title: Deep neural networks and their implementation

Author: Bc. Ján Vojt

Department: Department of Theoretical Computer Science and Mathematical

Logic

Supervisor: doc. RNDr. Iveta Mrázová CSc., Department of Theoretical Computer Science and Mathematical Logic

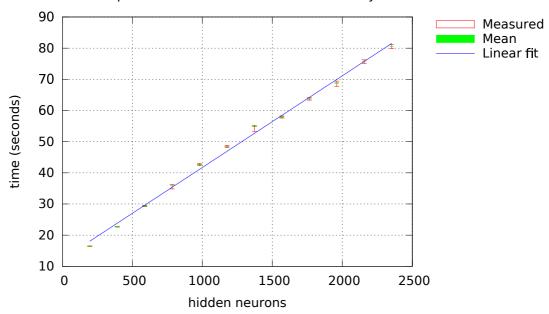

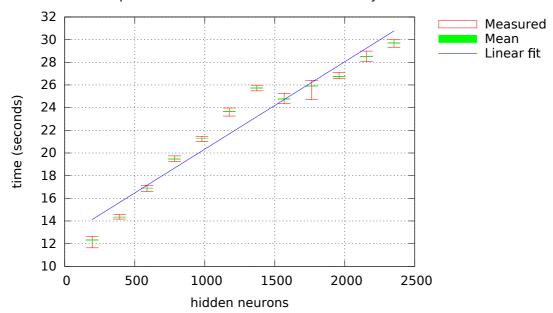

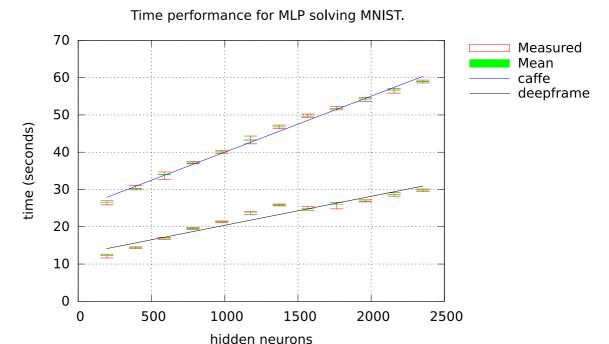

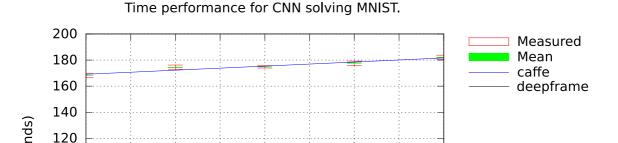

Abstract: Deep neural networks represent an effective and universal model capable of solving a wide variety of tasks. This thesis is focused on three different types of deep neural networks – the multilayer perceptron, the convolutional neural network, and the deep belief network. All of the discussed network models are implemented on parallel hardware, and thoroughly tested for various choices of the network architecture and its parameters. The implemented system is accompanied by a detailed documentation of the architectural decisions and proposed optimizations. The efficiency of the implemented framework is confirmed by the results of the performed tests. A significant part of this thesis represents also additional testing of other existing frameworks which support deep neural networks. This comparison indicates superior performance to the tested rival frameworks of multilayer perceptrons and convolutional neural networks. The deep belief network implementation performs slightly better for RBM layers with up to 1000 hidden neurons, but has a noticeably inferior performance for more robust RBM layers when compared to the tested rival framework.

Keywords: multilayer neural networks, convolutional neural networks, deep belief networks

Název práce: Hluboké neuronové sítě a jejich implementace

Autor: Bc. Ján Vojt

Katedra: Katedra teoretické informatiky a matematické logiky

Vedoucí bakalářské práce: doc. RNDr. Iveta Mrázová CSc., Katedra teoretické informatiky a matematické logiky

Abstrakt: Hluboké neuronové sítě jsou efektivní a univerzální model schopný řešit širokou škálu úloh. Tato práce je zaměřena na studium tří různých typů hlubokých neuronových sítí – vícevrstvý perceptron, konvoluční neuronové sítě, a sítě typu DBN (deep belief). Všechny popisované modely hlubokých neurónových sítí jsou naimplementovány na paralelní hardvérové architektuře, a otestovány pro různa nastavení architektury sítě i jejích parametrů. Implementovaný systém je doplněn detailní dokumentací softvérového návrhu a popisem použitých optimalizací. Efektivitu implemenetovaného frameworku dokládají i výsledky provedených výkonnostních testů. Významnou součást práce představuje i testování dalších existujících frameworků s podporou hlubokých neuronových sítí. Porovnání ukazuje, že framework vytvořený v rámci této práce dosáhl lepších výkonnostních výsledků než testované konkurenční implementace vícevrstvých perceptronů a konvolučních neuronových sítí. Implementace sítí typu DBN dosahuje v porovnání s konkurenční implementací mírně lepších výkonnostních výsledků pro RBM vrstvy o velikosti do 1000 neuronů, ale znatelně slabších výkonnostních výsledků pro robustnější RBM vrstvy.

Klíčová slova: vrstevnaté neuronové sítě, konvoluční neuronové sítě, hluboké sítě

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor doc. RNDr. Iveta Mrázová, CSc for her guidance, the considerable time spent on consultations, proof reading, and for inspiring me to start the work on this thesis in the first place.

I would like to acknowledge the academic and technical support of the Charles University in Prague, namely for the provided hardware used for evaluating various deep learning frameworks. Additionally, I would like to thank Mgr. Pavel Semerád for maintaining the provided machines, and for promptly resolving the arose issues.

Special thanks to Mgr. Jana Hajduová, whose patience and support gave me the strength to work on this thesis.

# Table of Contents

| 1 | $\operatorname{Intr}$ | oduction                                         | 3  |

|---|-----------------------|--------------------------------------------------|----|

|   | 1.1                   | Motivation                                       | 4  |

|   | 1.2                   | Methodology                                      | 4  |

|   | 1.3                   | Thesis structure                                 | 5  |

| 2 | Art                   |                                                  | 7  |

|   | 2.1                   | 1                                                | 9  |

|   | 2.2                   | v 1 1                                            | 9  |

|   |                       | 01                                               | 0  |

|   |                       | 1 1 0                                            | 4  |

|   | 2.3                   |                                                  | 6  |

|   |                       |                                                  | 6  |

|   |                       | v                                                | 7  |

|   |                       | 1 0 0                                            | 20 |

|   |                       | 1 1 0                                            | 21 |

|   |                       |                                                  | 21 |

|   |                       | 2.3.4.2 Backpropagation in convolutional layer 2 | 22 |

|   | 2.4                   | 1                                                | 23 |

|   |                       |                                                  | 23 |

|   |                       |                                                  | 24 |

|   |                       |                                                  | 25 |

|   |                       | 2.4.4 Training Restricted Boltzmann Machines     |    |

|   |                       | 2.4.4.1 Contrastive Divergence                   | :7 |

|   |                       | O                                                | 28 |

|   |                       | 1                                                | 28 |

|   |                       | 2.4.6 Training a Deep Belief Network             | :9 |

| 3 | Imp                   | lementation 3                                    | 1  |

|   | 3.1                   | Parallel computing platforms                     | 1  |

|   |                       | 3.1.1 FPGA                                       | 2  |

|   |                       | 3.1.2 NVIDIA CUDA                                | 34 |

|   |                       |                                                  | 34 |

|   |                       | 1                                                | 34 |

|   | 3.2                   | Requirements                                     | 6  |

|   | 3.3                   | Architecture                                     | 37 |

|   | 3.4                   | 1                                                | 8  |

|   | 3.5                   | Network configuration                            |    |

|   |                       | v e                                              | 13 |

|   | 3.6                   |                                                  | 15 |

|   | 3.7                   | 1                                                | 6  |

|   |                       |                                                  | 6  |

|   |                       |                                                  | 17 |

|   |                       | v                                                | 18 |

|   |                       | 3.7.4 Error computing module                     |    |

|   |                       | 3.7.5 Training module                            | 0  |

|              |                                   | 3.7.6                                    | Logging module                    | 50 |  |

|--------------|-----------------------------------|------------------------------------------|-----------------------------------|----|--|

|              | 3.8 Multilayer perceptron network |                                          |                                   | 52 |  |

|              | 3.9                               |                                          |                                   |    |  |

|              | 3.10                              |                                          | pelief network                    | 56 |  |

| 4            | Test                              | ing                                      |                                   | 61 |  |

|              | 4.1                               | Testing                                  | g requirements                    | 61 |  |

|              | 4.2                               |                                          |                                   |    |  |

|              |                                   | 4.2.1                                    | Hardware specification            | 62 |  |

|              |                                   | 4.2.2                                    | Software specification            | 63 |  |

|              | 4.3                               | Testing                                  | g methodology                     | 64 |  |

|              | 4.4                               | Multila                                  | ayer Perceptron                   | 66 |  |

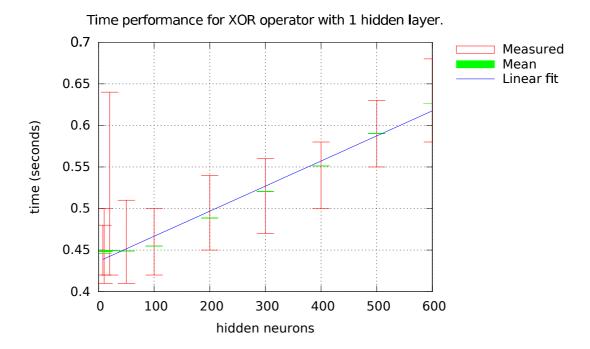

|              |                                   | 4.4.1                                    | Exclusive OR operator             | 66 |  |

|              |                                   | 4.4.2                                    | The sum of two four-bit numbers   | 69 |  |

|              |                                   | 4.4.3                                    | Recognition of handwritten digits | 70 |  |

|              | 4.5                               | Convo                                    | lutional Neural Network           | 73 |  |

|              |                                   | 4.5.1                                    | Recognition of handwritten digits | 74 |  |

|              | 4.6                               | Deep I                                   | Belief Network                    | 76 |  |

|              |                                   | 4.6.1                                    | Recognition of handwritten digits | 76 |  |

|              | 4.7                               | Comparison with other testing frameworks |                                   |    |  |

|              |                                   | 4.7.1                                    | Caffe framework                   | 79 |  |

|              |                                   | 4.7.2                                    | Theano                            | 81 |  |

| 5            | Con                               | clusior                                  | n                                 | 85 |  |

|              | 5.1                               | Furthe                                   | er work                           | 86 |  |

| Bibliography |                                   |                                          | 87                                |    |  |

| Glossary     |                                   |                                          | 91                                |    |  |

| Attachments  |                                   |                                          |                                   | 95 |  |

# 1. Introduction

The first known computational model of neural networks was formalized in 1943 by neurophysiologist Warren McCulloch and mathematician Walter Pitts [25]. Their work discusses how neurons in the brain might work. Their mathematical model marks the creation of a new field of study - Artificial neural networks (ANNs). The motivation for the research at this point in time was to provide an insight into the functionality of the brain.

A decade later, computers became powerful enough to simulate a hypothetical neural network. Eventually, researchers realized the pattern-matching and learning capabilities of neural networks could allow them to address a variety of problems which were difficult to be solved effectively using conventional methods and algorithms.

The first neural network model solving a real-world problem was developed by Bernard Widrow and Marcian Hoff of Stanford in 1959. Its name was ADALINE, and could recognize binary patterns. While reading a stream of bits from a phone line, it could predict the next bit, which could eliminate echoes from the stream. The research slowed down in the 1960's, because of the book Minsky and Papert published. They demonstrated that the simple two-layer perceptron is incapable of usefully representing or approximating functions outside a very narrow class [26]. Although they left the possibility of better performance open, their claims halted research of multilayer feed-forward networks for several years.

The 1980's brought a boom in the field, and showed that some of the perceptron limitations may be overcome [18]. This is mainly attributed to the back-propagation algorithm. It was invented a decade sooner, but the first computer experiments demonstrating it can generate useful representations were published in 1986 [29]. As a consequence, artificial neural networks proved to be a powerful tool able to solve complex problems such as perception, concept learning, the development of motor skills, voice recognition, etc.

The boom in the field continued throughout 1990's, however there was still a problem with the performance. Building more robust networks took weeks, even months to train on contemporary hardware. The situation changed after leveraging new learning algorithms and parallel computing to speed up the learning process. It allowed to construct deeper ANN models capable of recognizing very complex and abstract patterns.

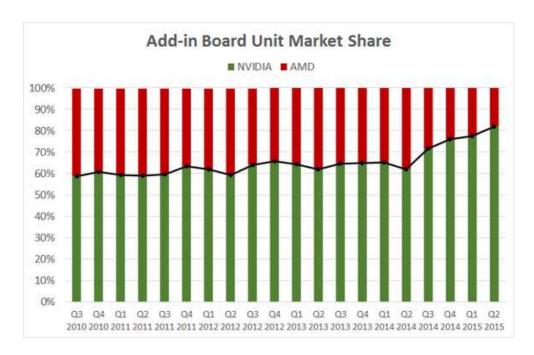

The parallel architecture found its use in the gaming industry. Gamers represented a big market, which provided generous funding for developing high-performance chips with parallel architecture. In the past decade, these high performance chips became relatively cheap, and hence available for masses. This greatly fueled the research in the artificial intelligence field.

The achievements are astonishing. Artificial neural networks found applications in a wide range of fields. To name a few examples, they are used in medicine to identify brain structures in magnetic resonance images [24], in geology to analyze 3D seizmic data volumes [33], in energetics for forecasting regional electricity loads [19], or in logistics for driving trucks [2]. Autonomous navigation cars are currently being researched [21] and tested heavily, but the most apparent obstacles today are legal barriers. Although in some states, autonomous cars are

already legal today (Nevada, Assembly Bill 511, 2011). Their use is about to revolutionize the transportation of people and goods.

#### 1.1 Motivation

Artificial neural networks are proving themselves to be a very effective and extremely universal tool. All the above examples of usefulness and effectiveness of artificial neural networks are showing a very promising future for their use. In the past decade they were almost exclusively a domain of revolutionary companies with virtually unlimited resources funding their research, like Google, Facebook, Netflix, etc. However today, the methods of artificial intelligence seem to shape as an indivisible part of any successful venture in the industry. Some experts even predict that artificial intelligence will lead to the next industrial revolution.

The main objectives of this thesis are to discuss the theory behind deep artificial neural networks, design and build a high-performance implementation using parallel architecture, and evaluate the obtained performance results. The network architectures studied and implemented will comprise the multilayer perceptron network, the convolutional neural network, and the deep belief network. This work is not focused on solving any specific problem, but is rather universal. The resulting implementation, however, should be very flexible in terms of the ability to create any desired network architecture, and in terms of configuring the network parameters. This will allow the users to model neural networks capable of solving any specific task at hand.

# 1.2 Methodology

The outcome of this work will be an implemented framework for modeling artificial neural networks. The supported network types will be the previously mentioned multilayer perceptron network, the convolutional network, and the deep belief network. The framework will provide a simple but user friendly approach to configuring the specific network architecture, and the network and training parameters. All the configuration options will be accessible without the need of recompiling the framework itself. This is an important property, as it will not require the users to understand and edit the code.

The evaluation of the implemented framework will also form an important part of this work. It will be done via automated test cases with different network architectures and parameters. These test cases will be defined as code, so that anyone can rerun the tests in the future and verify the achieved results. An important part of the evaluation will also be a comparison with other available frameworks capable of working with the above mentioned neural network types. These test cases will also be automated and defined as code for all of the frameworks. This will again guarantee repeatable and verifiable results.

All the test cases along with the results will be included in the optical disk attached to the physical copies of the thesis.

#### 1.3 Thesis structure

This thesis consists of three chapters. The first chapter provides the theoretical background for the studied artificial neural networks. The second chapter documents the implemented framework for working with the supported neural network types. The last chapter presents the evaluation of the implemented framework.

The first chapter with the theory behind artificial neural networks explains the structure of a neuron as the fundamental building block of the network. It also discusses the universal concepts reused in all the implemented network types. In the following sections, this chapter defines each of the studied network types. It also describes the training process for each network type separately.

The second chapter compares the available parallel hardware architectures and discusses whether they are suitable for implementing artificial neural networks. The decision regarding the chosen hardware platform is made, along with explaining the supporting arguments. The chapter continues with a detailed description of the software architecture and the decisions made during framework implementation. The installation procedure and the configuration options can be also found here. The chapter concludes with the specifics in the implementation of each network type.

The last chapter begins with testing requirements before explaining the testing methodology. It continues with the presentation of the results obtained from testing. The last two sections in this chapter compares the implemented framework to other existing frameworks for working with deep neural networks. The results are presented in graphs comparing the time performance of each tested framework with the same network configuration and on the same hardware.

# 2. Artificial neural networks

Inspired by biological nervous systems, artificial neural networks (ANNs) aim at reaching their versatility through learning. ANNs are commonly employed in artificial intelligence, machine learning and pattern recognition. There has been substantial research into how the human brain's structure achieves such a high level of versatility. This research has provided some important insights, however the conclusions are far from completely explaining the complex functioning of the brain. Even though we have not been able to replicate the brain so far, the field of artificial intelligence offers very effective solutions to many problems by simulating the observations of biological research of various nervous systems.

It is estimated, that the average human brain contains 86 billion neurons [13]. Together they form a huge network. Even if we knew the detailed inner structure of the human brain, we would still not be able to simulate it with current technology because of its robustness. Our efforts are therefore rather different. We want to build a neural network with a good ratio between its size and its effectiveness.

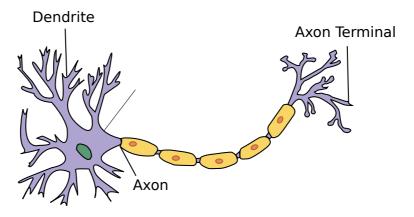

Figure 2.1: Model of a biological neuron. Image was taken from Wikipedia, where it is published under Creative Commons BY-SA 3.0 license. Image was adapted.

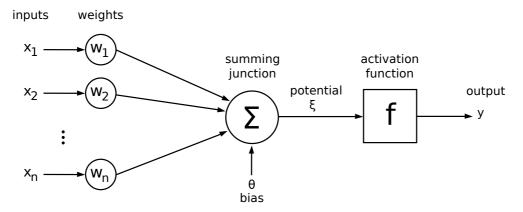

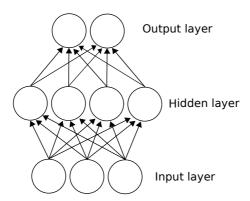

Generally, ANNs consist of a set of artificial neurons. Formally, an artificial neuron has n inputs represented as a vector  $\vec{x} \in \mathbb{R}^n$ . Inputs in an artificial neuron correspond to the dendrites in a biological neuron, while a single output of an artificial neuron corresponds to the axon in a biological neuron, which is depicted in Figure 2.1. Each input  $i, 1 \leq i \leq n$ , has an assigned weight  $w_1, \ldots, w_n$ . Weighted input values are combined and run through an activation function producing some output y, as shown in Figure 2.2. The network is formed by connecting the neuron output with the input of a different neuron. ANN is therefore effectively described as an oriented graph as shown in Figure 2.4, where vertices represent the neurons, and oriented edges represent the output-input connections between them.

A set of input neurons consists of the neurons which are the first ones in any complete path in the graph. All input neurons have exactly one input, and all inputs together represent an instance of the problem to be solved by the ANN. A set of output neurons consists of the neurons which are the last ones in any complete path in the graph. All output neurons have exactly one output, and

all outputs together represent a possible solution to the problem to be solved by the ANN. A set of hidden neurons consists of the neurons which are not input, nor output neurons. Their number and organization into layers may vary even for the same problem, but is a key feature of the network vastly influencing its performance.

An ANN works by feeding the data into the input neurons. The data flows in the direction of oriented edges and ends when the output neurons are hit. The result is interpreted from the values obtained in the output neurons.

Figure 2.2: Model of an artificial neuron.

Formally, an ANN is a 6-tuple M = (N, C, I, Y, w, t), where

- $\bullet$  N is a finite non-empty set of neurons,

- $C \subseteq N \times N$  is a non-empty set of oriented edges between the neurons,

- $X \subset N$  is a non-empty set of neurons in the input layer,

- $Y \subset N$  is a non-empty set of neurons in the output layer,

- $w: C \mapsto \mathbb{R}$  is a weighting function,

- $t: N \mapsto \mathbb{R}$  is a function for network bias.

Let us consider neuron j with its input  $\vec{x_j} = (x_{1j}, \dots, x_{nj})$ , weights  $w_{1j}, \dots, w_{nj}$  and bias  $\theta_j$ . Then the potential of the neuron is computed:

$$\xi_j = \sum_{i=1}^n w_{ij} x_{ij} + \theta_j. \tag{2.1}$$

Consider the following activation function:

$$f(\xi_j) = \frac{1}{1 + e^{-\xi_j}}. (2.2)$$

Then the output  $y_i$  of the neuron j is computed:

$$y_j = f(\xi_j) = f\left(\sum_{i=1}^n w_{ij} x_{ij} + \theta_j\right).$$

(2.3)

Considering ANN containing m such neurons in the output layer, we obtain the output of the network as  $\vec{y} = (y_1, \dots, y_m)$ .

A more general definition is given by Atencia, Joya and Sandoval [1], where ANN is defined as a dynamic system whose state, at a given instant, is characterized by M. Network states are referred to as configurations. During the learning process, ANNs may change their weights, bias, or in some networks even the number of neurons and their setup. In contrast, our definition does not allow such modifications and M does not change in the process of learning.

# 2.1 Perceptron

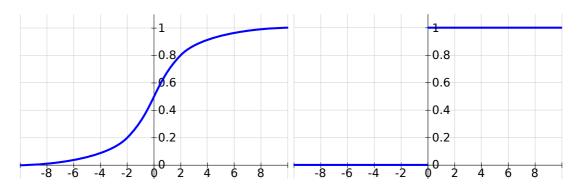

The most trivial neural network is the perceptron that consists of one fully functional neuron only. Its output is calculated directly by Equation 2.3. In Figure 2.3 we can see the most commonly used activation functions: sigmoid (Eq. 2.2) and unit step function. The output of the sigmoid function produces continuous output, while the unit step function produces strictly binary outputs. By the standard definition, the single perceptron forming a trivial network uses step function exclusively.

Figure 2.3: Graph of the sigmoid and the unit step function.

ANNs consisting of a single perceptron neuron are too trivial for complex tasks. However, they can be combined into a multilayer perceptron network (MLP) to address a wider set of problems. As we will see in Section 2.2.1 discussing training of an MLP, continuous functions are more suitable for gradient-based learning, because we can calculate their derivative. This is important to easily determine the weight adjustment rules.

# 2.2 Multilayer perceptron

The Multilayer perceptron (MLP) is a feed-forward neural network consisting of multiple mutually interconnected layers of neurons. The layers are stacked one onto each other. Every neuron in one layer is connected to every neuron in the following layer. The motivation behind designing multilayer networks is to be able to solve more complex tasks. The MLP network is built of perceptrons defined in Section 2.1. The unit step function is usually not a suitable activation function to be used with the perceptrons. Because of continuity and greater flexibility, the sigmoidal function is most commonly used instead. When choosing the most suitable activation function, we want it to be differentiable at every point of its

domain, and to be non-linear. Non-linearity is important, because in general we want the output to be non-linearly dependent on the given input.

Perceptrons are arranged into  $\kappa \geq 2$  layers. Let us consider a network M with  $\kappa$  layers. The set of neurons C is split into mutually disjunct subsets called layers  $L_1, \ldots, L_{\kappa}$ . More formally it holds  $\forall i, j : 1 \leq i, j \leq \kappa$   $(L_i \neq \emptyset \land L_i \cap L_j \neq \emptyset) \Rightarrow i = j$ . The network layers are stacked one onto each other,  $L_1$  being the input layer,  $L_2, \ldots L_{\kappa-1}$  being the hidden layers and  $L_{\kappa}$  being the output layer. As shown in Figure 2.4, the edges are all oriented in the direction from the input layer  $L_1$  towards the output layer  $L_{\kappa}$ . Each neuron in layer  $L_i$  is connected to every neuron in layer  $L_{i+1}$ . In other words all neighboring layers form complete bipartite graphs.

Figure 2.4: A Multilayer perceptron network consisting of 3 layers.

The output of the network is computed sequentially, layer by layer. We start with the input layer by directly assigning  $\vec{y}^0 = \vec{x}$ . Then the computation proceeds by assigning input  $\vec{x}^i = \vec{y}^{i-1}$  for layer  $L_i$ . The weights and the activation function are given by the network, thus the output of each layer depends only on the output of the previous layer. The final output of the network is then produced as  $\vec{y}^k$  in the output layer  $L_{\kappa}$ .

# 2.2.1 The training process

The ability to learn is the key concept of neural networks. The aim of the process is to find the optimal parameters (and structure) of the network for solving the given task. Before the training process starts, network parameters need to be initialized. Initial values are often chosen randomly, however using some heuristics may lead to a faster parameter adjustment towards the optimal values. Learning is then carried out on the training set by feeding the training data through the network. It is an iterative process, where the outputs produced on each input from the training set are analyzed and the network is repeatedly being adjusted to produce better results. The network is considered to be trained after reaching the target performance on the training data. There exist different metrics for assessing the network performance. I will use the mean squared error, which I will define formally in the following text (Eq. 2.7).

In this thesis I will focus on learning from a labelled dataset. Such dataset consists of input patterns for the network with their corresponding labels - expected network outputs. The process of learning from the labelled dataset is

reffered to as supervised learning. If the data labels are not available, it is possible to employ unsupervised learning using specialized algorithms, which will not be discussed here.

A common problem encountered in the process of learning is overfitting. It generally occurs when the learning is performed for too long, and especially when the training set is too small to evenly represent all types of patterns from the domain of possible network inputs. In such a case the learning may adjust the network to random features present in the training data. Overfitting is observed during the learning process, when network's predictive performance is improving on the training set, however worsening on previously unseen test data.

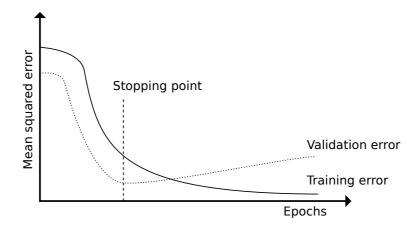

To combat this issue the labeled data is split into a training and a validation set. The main reason why to use the validation set is that it shows the error rates on the data independent from the data we are training on. A study by Guyon suggests that the optimal ratio between the size of training vs. validation data set depends on the number of recognized classes and the complexity of class features [11]. An estimation of feature complexity is however quite cumbersome. A good starting point for determining this ratio is to put 80% of the available data into the training set and 20% into the validation set. Further experimentation may help to move closer to the optimal ratio. While learning, the performance of the ANN is regularly examined on validation data set. When errors retrieved on validation data reach a stopping point, learning process is stopped (see Figure 2.5) and the network is considered trained.

Figure 2.5: Graph comparing the evolution of the training error vs. the validation error.

To define the learning process formally and in more detail, let us consider P training patterns labeled  $(\vec{x}^p, \vec{d}^p)$ , where  $\vec{x}^p$  is the input vector,  $\vec{d}^p$  is the desired output vector, and  $1 \leq p \leq P$ . Given the current configuration of the network, the input  $\vec{x}^p$  yields the output  $\vec{y}^p$ . Then for every pattern p we want  $\vec{y}^p$  to be as close to the desired output  $\vec{d}^p$  as possible. We can define the error of each neuron j in the output layer as:

$$e_j^p = y_j^p - d_j^p. (2.4)$$

Now we can define the squared error for pattern p as:

$$E_p = \frac{1}{m_{\kappa}} \sum_{j=1}^{m_{\kappa}} \left( e_j^p \right)^2 = \frac{1}{m_{\kappa}} \sum_{j=1}^{m_{\kappa}} \left( y_j^p - d_j^p \right)^2, \tag{2.5}$$

where  $m_{\kappa}$  is the number of neurons in the output layer. Note that if the actual output is exactly the same as the desired output, we get zero for the squared error. In other words the following holds true:

$$\forall j : E_p = 0 \Leftrightarrow e_i^p = 0 \Leftrightarrow y_i^p = d_i^p. \tag{2.6}$$

It may be useful to sum up the average error for all input patterns to assess the network performance on the whole dataset, which can be achieved simply by computing the mean squared error [12, pp. 183]:

$$E_{avg} = \frac{1}{P} \sum_{p=1}^{P} E_p. \tag{2.7}$$

When learning, for each interconnected pair of neurons (i, j), where i is a neuron in layer l, j is a neuron in layer l + 1 and  $w_{i,j}$  weights their connection, we want to adjust  $w_{i,j}$  to minimize the mean squared error  $E_{avg}$ . Provided the activation function is differentiable everywhere on its domain,  $E_{avg}$  is also differentiable. When adjusting the weight  $w_{i,j}$  of the neuron j located in the output layer  $\kappa$ , we are therefore interested in the partial derivative:

$$\frac{\partial E_{avg}}{\partial w_{i,j}} = \frac{1}{P} \frac{\partial}{\partial w_{i,j}} \sum_{p=1}^{P} E_p = \frac{1}{P} \sum_{p=1}^{P} \frac{\partial E_p}{\partial w_{i,j}}.$$

(2.8)

To be able to adjust the network after each presented input pattern, we are actually interested in the derivative for each given pattern p and its corresponding  $E_p$ . In the following equations we will therefore omit the pattern index p. Applying the chain rule to Equation 2.8 we get:

$$\frac{\partial E}{\partial w_{i,j}} = \frac{\partial E}{\partial y_j} \frac{\partial y_j}{\partial w_{i,j}}.$$

(2.9)

Using Equation 2.5 we can evaluate the first factor as:

$$\frac{\partial E}{\partial u_i} = (y_j - d_j). \tag{2.10}$$

Then we evaluate the second factor:

$$\frac{\partial y_j}{\partial w_{i,j}} = \frac{\partial y_j}{\partial \xi_j} \frac{\partial \xi_j}{\partial w_{i,j}} = f'(\xi_j) \frac{\partial}{\partial w_{i,j}} \sum_k w_{k,j} y_k = f'(\xi_j) y_i. \tag{2.11}$$

By combining both evaluated factors we get:

$$\frac{\partial E}{\partial w_{i,j}} = (y_j - d_j) f'(\xi_j) y_i. \tag{2.12}$$

For convenience Haykin defines the so-called local gradient  $\delta_j$  for neuron j in the output layer [12, pp. 185] as the following relation:

$$\delta_{j} = \frac{\partial E}{\partial \xi_{j}} = \frac{\partial E}{\partial y_{j}} \frac{\partial y_{j}}{\partial \xi_{j}} = (y_{j} - d_{j}) f'(\xi_{j}). \tag{2.13}$$

Then we can reformulate Equation 2.12 into:

$$\frac{\partial E}{\partial w_{i,j}} = \delta_j y_i. \tag{2.14}$$

Using Equation 2.14 we can compute the gradient of the error function for each of the given patterns p. We need to adjust the weight  $w_{i,j}$  proportionally to the gradient but in the opposite direction. However doing so for every input pattern would produce a very unstable system. To combat this problem we can use a learning parameter  $0 < \eta < 1$ . The weight adjustment is then computed by:

$$\Delta w_{i,j} = -\eta \frac{\partial E}{\partial w_{i,j}} = -\eta \delta_j y_i. \tag{2.15}$$

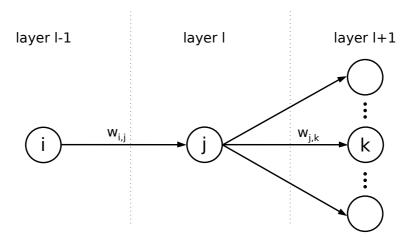

The weight adjustment  $\Delta w_{i,j}$  in 2.15 is only applicable to the neurons in the output layer. Computation of the adjustment for neurons in the hidden layers is more complicated. For instance, consider 3 neurons i, j, and k, all following each other on the same path along the layers l-1, l and l+1, respectively, as illustrated in Figure 2.6. Then the adjustment of  $w_{i,j}$  needs to be done carefully, because besides influencing the output of neuron i itself, it also impacts all the outputs (and thus errors) in all layers following l. Minding this, let us bring our attention to the the layers l < L in the following text.

Figure 2.6: Illustration showing how a change in the weight  $w_{i,j}$  of the neuron in the hidden layer l-1 influences the weight  $w_{j,k}$  of the neuron in the following layer l.

Note that Equation 2.12 still applies to hidden layers. However, we need to look at the definition of the local gradient again. In the previous Equation 2.13 we are using the desired output  $d_j$  to calculate  $\partial E/\partial y_j$ . Of course, there is no desired output known in hidden layers. It is actually dependent on the network design. Because of this, we need to step back and use the following definition for  $\delta_j$ :

$$\delta_{j} = \frac{\partial E}{\partial \xi_{j}} = \frac{\partial E}{\partial y_{j}} \frac{\partial y_{j}}{\partial \xi_{j}} = \frac{\partial E}{\partial y_{j}} f'(\xi_{j}). \qquad (2.16)$$

Now we need to redefine  $\partial E/\partial y_j$  for hidden layers. For any hidden layer l, the following layer l+1 must exist (otherwise l would be the output layer). Given the neurons i, j and k each in a different layer as illustrated in Figure 2.6, we can use the potential  $\xi_k$ .

$$\frac{\partial E}{\partial y_j} = \sum_{k=1}^{m_{l+1}} \frac{\partial E}{\partial \xi_k} \frac{\partial \xi_k}{\partial y_j} = \sum_{k=1}^{m_{l+1}} \frac{\partial E}{\partial \xi_k} w_{j,k} = \sum_{k=1}^{m_{l+1}} \delta_k w_{j,k}$$

(2.17)

Combining equations 2.16 and 2.17 we get:

$$\delta_j = \left(\sum_{k=1}^{m_{l+1}} \delta_k w_{j,k}\right) f'\left(\xi_j\right). \tag{2.18}$$

Equation 2.18 tells us, that knowing the local gradient of neuron k in layer l+1, we can calculate the local gradient for neuron j in layer l. This fact will allow us to recursively adjust the network weights going layer by layer in the direction from the output to the input (backwards). It is used in the most common learning algorithm discussed in Section 2.2.2.

Finally, we can summarize the weight adjustment applicable to all the layers in a given network:

$$\Delta w_{i,j} = -\eta \frac{\partial E}{\partial w_{i,j}} = -\eta \delta_j y_i, \qquad (2.19)$$

where

$$\forall j \text{ in layer } l < L \qquad \delta_j = \left(\sum_{k=1}^{m_{l+1}} \delta_k w_{j,k}\right) f'(\xi_j)$$

$$\forall j \text{ in layer } L \qquad \delta_j = \left(y_j - d_j\right) f'(\xi_j) \tag{2.20}$$

# 2.2.2 Backpropagation algorithm

The purpose of the backpropagation algorithm is to adjust the synaptic weights of neurons, so that the network produces the desired output. The algorithm describes the process of training (also called learning). The result of this algorithm is a neural network configured to minimize the error when solving given problem.

Training must be performed on labeled data and therefore is supervised. Before the algorithm starts, the weights need to be initialized to some values. The initialization is not a part of the algorithm specification, as there may be different approaches, the most common being the most trivial - random initialization. Then the training algorithm starts.

Each input pattern with its class label  $(\vec{x}_p, \vec{d}_p)$  is sequentially processed in two phases. The first phase called the forward phase puts the input pattern as the input of the network, setting  $\vec{y}^0 = \vec{x}_p$ . The network then computes its output  $\vec{y}^L$ . The sole purpose of the forward phase is to calculate the output for the presented pattern, and the network is not adjusted at all. At this point the backward phase starts. The purpose of this phase is to adjust the network weights to achieve a better assessment of the input data.

Learning is performed in multiple epochs. In each epoch, all the data from the training set is processed. The duration of an epoch directly depends on the size of the network and the size of the training set, as each input pattern from the training set is processed exactly once. However the number of epochs is not limited. An important decision of the learning process is therefore the determination of the stopping criterion. After each epoch we validate the error on the validation data set. Once this error starts to increase, we achieved some (local or perhaps global) minimum, and it is usually wise to stop the learning process at this point (see Figure 2.5).

Formally, the backpropagation algorithm will be described below:

#### Input:

- training patterns  $(\vec{x}^p, \vec{d}^p), 1 \leq p \leq P$

- validation patterns  $(\vec{v}^q, \vec{d}^q), 1 \leq q \leq Q$

- activation function f and its derivation  $f'(\xi)$

- e.g. the sigmoidal function:  $f(\xi) = 1/(1 + e^{-\xi})$ ;  $f'(\xi) = f(\xi)(1 f(\xi))$

- learning parameter  $\eta \in (0,1)$

- $\bullet$  feed-forward neural network M with randomly initialized weights

#### Output:

• a trained feed-forward neural network M'

#### Algorithm:

- 1. Set  $E_{avg} = \infty$ .

- 2. Start a new epoch.

- 3. For each  $p \in \{1, ..., P\}$  present the pattern  $(\vec{x}^p, \vec{d}^p)$ .

- Set  $\vec{y}^0 = \vec{x}^p$ .

- forward phase

- For  $l=1,2,\ldots,\kappa$  compute the output of M for  $\vec{x}^p$  in the following way:

$$\forall j \in L_l \text{ compute } \xi_j = \sum_{i=1}^n w_i x_i + \theta \text{ and } y_j = f(\xi).$$

- backward phase

- $\forall i \in L_{\kappa-1}, j \in L_{\kappa} \text{ compute } \delta_j = (y_j d_j^p) f'(\xi_j) \text{ and } \Delta w_{i,j} = -\eta \delta_j y_i.$

- For  $l=\kappa-1,\ldots,1$  do

- $\forall i \in L_{l-1}, j \in L_l \text{ compute } \delta_j = \sum_{k=1}^{m_{l+1}} \delta_k w_{j,k} f'(\xi_j), \ \Delta w_{i,j} = -\eta \delta_j y_i.$

- For  $l = 1, 2, ..., \kappa \ \forall (i, j) \in L_{l-1} \times L_l \text{ adjust } w_{i,j} \text{ by } \Delta w_{i,j}$ .

- Compute the error for the pattern p:  $E_p = 1/m_\kappa \sum_{j=1}^{m_\kappa} (y_j^p d_j^p)^2$ .

- 4. Set  $E_{prev} = E_{avg}$  and compute new  $E_{avg} = 1/P \sum_{p=1}^{P} E_p$  for the validation data set.

- 5. If  $E_{avg} < E_{prev}$  go to step 2.

- 6. Finish.

#### 2.3 Convolutional neural networks

Convolutional neural networks (CNNs) are multi-layer feed-forward networks specifically designed to recognize features in 2-dimensional image data. The architecture of CNNs is inspired by Hubel and Wiesel's study of neurobiological signal processing in cat's visual cortex [20]. A typical application of CNNs consists of recognition of various objects in images. However convolutional networks have been successfully used for various different tasks [7] [6], too.

CNNs are primarly used for 2D image recognition, so we will illustrate their architecture on a 2D rectangular image consisting of pixels. Each pixel generally carries colour information. Colour can be represented by multiple channels (e.g. 3 RGB channels). For the sake of simplicity, we will consider only one single channel (shades of gray) while explaining the model.

The neurons in CNNs work by considering a small portion of the image, let us call it subimage. The subimages are then inspected for features that can be recognized by the network. As a simple example, a feature may be a vertical line, an arch, or a circle. These features are then captured by the respective feature maps of the network. A combination of features is then used to classify the image. Furthermore, multiple different feature maps are used to make the network robust to varying levels of contrast, brightness, colour saturation levels, noise, etc.

There are two types of layers, both consisting of feature maps. The purpose of the so-called convolutional layer is to recognize the features in the input image. It usually consists of several feature maps, each map recognizing certain feature. The subimages intentionally cover overlapping regions of the original image. Such a design is important in order to tolerate image distortions, like translation, rotation, skewing, etc.

The other layer type, the so-called subsampling layer, always follows after a convolutional layer. It consists of the same number of feature maps, where each map from the convolutional layer is used as an input for the corresponding feature map in the following subsampling layer. Subimages covered by the neurons from the subsampling layer usually do not overlap.

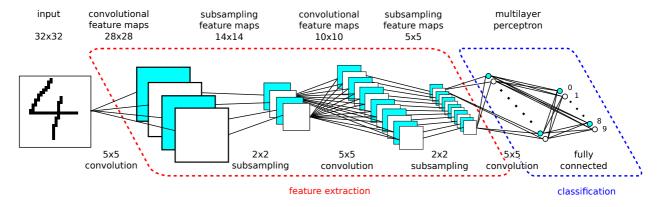

Depending on the network's depth, the convolutional and subsampling layers alternate until the last subsampling layer is reached. After the last subsampling layer, there may be any number of fully connected layers as described in Section 2.2, the last one of them is the output layer [22].

#### 2.3.1 Architecture of CNNs

To explain the architecture of the convolutional network, let us consider the image data in the input layer. From a high-level point of view, a convolutional network is architecturally split into two important parts. Each part is designed to fulfill a different purpose. The first part of the network performs feature extraction, and is built of convolutional and subsampling layers. The second part performs classification based on the extracted features. We will be using fully-connected MLP for this part.

Let us describe the feature extraction process in more detail. Starting with the presented input image, each pixel represents the input for the neurons grouped in

feature maps of the first convolutional layer. The neurons in the feature map are organized in a 2-dimensional grid. All the neurons within the same feature map share their weights. This allows to optimize the implementation by requiring less memory and yielding a better performance.

More importantly, it is an architectural feature. Each neuron in a given feature map is expected be recognize the same feature. The feature is recognized by a combination of weights, which are essentially filtering neural inputs. Sharing the same weights for all the neurons within the given feature map ensures the same filter is used for each pixel.

Let  $F_l$  be the set of feature maps in the layer l. All feature maps in  $F_l$  have the same size, let us denote it  $m_l \times n_l$ . Further,  $\forall 0 \le i < m_l, 0 \le j < n_l$  let  $y_{i,j}^{\phi,l}$  be the output of the neuron  $(i, j, \phi, l)$ , at the position (i, j) in the feature map  $\phi$  of the layer l.

Figure 2.7: Example architecture of a convolutional neural network designed for the classification of handwritten digits from the MNIST dataset.

We will consider the input image as the output of the layer with zeroth index, having the size of  $m_0 \times n_0$  pixels. Note that the input layer can be also considered as a subsampling layer with one single feature map. The input layer is then followed by alternating convolutional and subsampling layers. The neurons of the feature map  $\phi$  in the convolutional layer l take the input from the set of feature maps  $F'_{\phi,l}$ , located in the previous subsampling layer ( $\emptyset \neq F'_{\phi,l} \subset F_{l-1}$ ). The convolutional layer is then followed by a subsampling layer, which reduces the size of feature maps. The last subsampling layer ends the feature extraction process.

At this point the second part of the network begins the classification process. The classification is performed using a fully-connected MLP network, which classifies the inputs according to the extracted features. For an example of a CNN see Figure 2.7. In the following sections we will describe the convolutional and subsampling layers in more detail.

## 2.3.2 Convolutional layer

The purpose of convolutional layers is to detect the features in the presented images. It consists of multiple feature maps, each recognizing certain specific feature. The feature recognition can be thought of as running the subimage through a filter. The filtering is essentially done through weight adjustments.

A filter may highlight or suppress a pixel's potential based on the surrounding pixels. The filtering to use is determined automatically by the learning process via weight adjustments.

The number of feature maps in the convolutional layer is an important architectural decision to make when designing the convolutional network. The optimal value depends on the nature of the problem being solved. The best way to determine the number of feature maps is to experiment. As a rule of thumb, more complex images are recognized better using more features, while simple tasks produce better results using just a few features. In fact, if the chosen number of features is too big, the features learned will often be duplicated.

Let us consider a convolutional layer l with a set of feature maps  $F_l$ . In general, this layer is always preceded by a subsampling layer with a set of feature maps  $F_{l-1}$ . For the sake of simplicity, we will refer to a feature map in the convolutional layer as a convolutional map. A feature map in the subsampling layer will be referred to as a subsampling map.

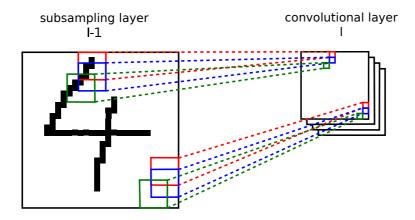

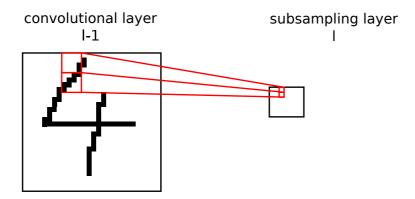

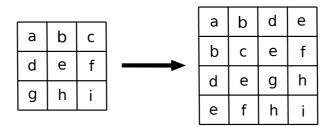

All feature maps in the same layer have the same size. The size of convolutional maps is predetermined by the size of subsampling maps in the preceding layer, by the layer parameter  $r_c^l$ , and by the overlapping parameter  $s_c^l$ . Each neuron in a convolutional map takes its input from  $(r_c^l)^2$  neurons in the corresponding subsampling map from the preceding layer. These input neurons form a square of dimension  $r_c^l \times r_c^l$ . The overlapping parameter  $s_c^l \ge 1$  determines how many neurons apart are these squares from each other, as can be seen in Figure 2.8. In the following text we will refer to this square of inputs as the receptive field of the neuron.

Figure 2.8: Illustration of the convolution operation on the input feature map of size  $28 \times 28$  neurons in layer l-1. The convolution uses a receptive field of size  $5 \times 5$  and overlapping parameter of 2 neurons, thus producing feature maps of size  $12 \times 12$  neurons in layer l. Note that neighboring neurons in convolutional layers have overlapping receptive fields.

As illustrated in Figure 2.8, neighboring neurons in a convolutional map have neighboring receptive fields that overlap in exactly  $(r_c^l - s_c^l)^2$  neurons. If the dimensions of the subsampling map are  $(m_{l-1}, n_{l-1})$ , the following convolutional maps must have the dimensions of:

$$(m_l, n_l) = \left( \left\lceil \frac{m_{l-1} - r_c^l + 1}{s_c^l} \right\rceil, \left\lceil \frac{n_{l-1} - r_c^l + 1}{s_c^l} \right\rceil \right). \tag{2.21}$$

Each neuron  $(i, j, \phi, l)$  is thus connected to all the neurons  $(is_c^l + \Delta i, js_c^l + \Delta j, \phi', l - 1)$  from the preceding layer, where  $\phi' \in F_{\phi,l}$  and  $0 \le \Delta i, \Delta j < r_c^l$ . Each connection within the receptive field of neuron  $(i, j, \phi, l)$  has the weight  $w_{\Delta i, \Delta j}^{\phi, \phi', l}$ . This weight is shared for all the neurons within the same feature map, i.e., for all i, j. At this point, we can compute the number of weights required by convolutional layer l. No matter what the dimensions of convolutional maps are, the total number of weights is:

$$|W_l| = |F_l| \cdot (r_c^l)^2. (2.22)$$

The output  $y_{i,j}^{\phi,l}$  and potential  $\xi_{i,j}^{\phi,l}$  of the neuron  $(i,j,\phi,l)$  are then computed as:

$$y_{i,j}^{\phi,l} = \xi_{i,j}^{\phi,l} = \sum_{\phi' \in F_{\phi,l-1}} \sum_{\Delta i=0}^{r_c^l - 1} \sum_{\Delta j=0}^{r_c^l - 1} y_{is_c^l + \Delta i, js_c^l + \Delta j}^{\phi',l-1} w_{\Delta i, \Delta j}^{\phi,\phi',l}.$$

(2.23)

The algorithm processing the convolutional layer l must sum the weights for each neuron. There are  $|F_l| \cdot m_l \cdot n_l$  neurons in layer l. Each of them must sum up  $|F_{l-1}| \cdot (r_c^l)^2$  weights (Eq. 2.22). This yields the following time complexity for processing the convolution in layer l.

$$O(|F_{l-1}| \cdot |F_l| \cdot (r_c^l)^2 \cdot m_l \cdot n_l) \tag{2.24}$$

Given the above definitions, there are 3 important parameters that need to be chosen to configure the convolutional layer.

- $|F_l|$ : the number of convolutional maps that will be corresponding to a single preceding subsampling map,

- $r_c^l$ : the receptive field size parameter,

- $s_c^l$ : the overlapping parameter.

As we already discussed, an adequate number of convolutional maps depends on the complexity of features in the classified input. We will test different values for a specific problem in Chapter 4.

The optimal value of the receptive field parameter also depends on the given problem. Its values are often small, so that the network can detect simple and small local features. The correct combination of the local features can then be trained. For instance, LeNet-5 network [22] uses  $r_c^l = 5$  for an input with  $m_0 = n_0 = 32$ .

The value of overlapping parameter is usually equal to 1. Increasing the parameter rarely makes sense, because if the receptive fields are too far apart, the network can miss important features. It might make sense to use higher overlapping parameter as an optimization technique for big images and big receptive fields. It is however disputable whether resampling the input images to a lower resolution would be a better approach. In our experiments in Chapter 4 we will be using relatively small input images, and therefore set this parameter to 1.

#### 2.3.3 Subsampling layer

The subsampling layer is either the first layer in the network (the input layer), or it follows after the convolutional layer. Let us consider a subsampling layer l consisting of a set of subsampling maps  $F_l$ . The purpose of the subsampling layer is to reduce the sizes of feature maps to simplify and generalize the recognized features.

Figure 2.9: Illustration of the subsampling operation on the input feature map of the size  $28 \times 28$  neurons from the layer l-1. In this case, the subsampling uses receptive fields of size  $4 \times 4$  neurons, thus producing feature maps of the size  $7 \times 7$  neurons in the layer l. Note, that in this illustrated case, the receptive fields of the subsampling neurons do not overlap.

Each convolutional map in layer l-1 is connected only to the corresponding subsampling map in layer l. The receptive fields of the subsampling neurons are specified by the parameters  $r_x^l$  and  $r_y^l$ , and usually do not overlap. Such a setting reduces the size of the feature maps by the factors  $r_x^l$  and  $r_y^l$  in each dimension, as illustrated in Figure 2.9. Formally, the new feature map sizes will be:

$$m_l = \left\lceil \frac{m_{l-1}}{r_x^l} \right\rceil \text{ and } n_l = \left\lceil \frac{n_{l-1}}{r_y^l} \right\rceil.$$

(2.25)

By this definition, each neuron from the convolutional layer is connected to exactly one neuron from the subsampling layer (and each convolutional map is connected to exactly one subsampling map). This results into a simple network design with the following time complexity when computing the output of the subsampling layer in the forward pass.

$$O(|F_{l-1}| \cdot m_{l-1} \cdot n_{l-1}) \tag{2.26}$$

Generally, the subsampling parameters can be chosen from the range  $1

ldots m_{l-1}$  for  $r_x^l$  and  $1

ldots n_{l-1}$  for  $r_y^l$ . The usual values are  $r_x^l = r_y^l = 2$ , which is the lowest value that makes sense. If the receptive fields should be out of the limits of the feature map bounds, their inputs will be simply considered to have the value of zero. It is effectively the same as if we padded the feature map with neurons with zero potential.

The neurons from the subsampling maps take their input from their receptive fields. Multiple inputs  $(r_x^l \times r_y^l)$  are then combined into a single value denoted as the neuron potential. The most common approaches to combine these inputs is

through averaging (Eq. 2.27), or finding the maximum value (Eq. 2.28). Having the feature map  $\phi$  in layer l, its output  $y_{i,j}^{\phi,l}$  is then multiplied by a trainable coefficient  $a^{\phi,l}$ , added to trainable bias  $b^{\phi,l}$ , and passed to an activation function f (Eq. 2.29).

$$\xi_{i,j}^{\phi,l} = \frac{1}{r_x^l r_y^l} \sum_{\Delta i=0}^{r_x^l - 1} \sum_{\Delta j=0}^{r_y^l - 1} y_{ir_x^l + \Delta i, jr_y^l + \Delta j}^{\phi,l-1}$$

(2.27)

$$\xi_{i,j}^{\phi,l} = \max_{\substack{\Delta i \in (0, r_x^l - 1) \\ \Delta j \in (0, r_x^l - 1)}} (y_{ir_x^l + dx, jr_y^l + dy}^{\phi, l - 1})$$

(2.28)

$$y_{i,j}^{\phi,l} = f(a^{\phi,l}\xi_{i,j}^{\phi,l} + b^{\phi,l})$$

(2.29)

#### 2.3.4 Backpropagation in Convolutional Networks

Convolutional networks are a kind of feed-forward networks. Hence it is possible to train them using the backpropagation algorithm. We will use the ideas and some definitions introduced in Section 2.2.1. The general objective will be the same - minimize the network error rate E through gradient descend technique. The weight adjustment will again start from the last layer. Using supervised learning, the expected neuron output is known here. We can use Equation 2.5 to compute the error  $E_p$  for the pattern p. We will be considering convolutional networks that have a conventional Multilayer Perceptron (MLP) as their last layer. The backpropagation process of MLP is defined in Section 2.2.2, and will be the same for this part of the convolutional network.

The details how to cope with different types of the network's lower layers will be discussed in the following subsections.

#### 2.3.4.1 Backpropagation in subsampling layers

The subsampling layer does not have any trainable weight parameters. In fact, its only trainable parameters are the coefficient  $a^{\phi,l}$  and bias  $b^{\phi,l}$ . As we are interested in the influence of these parameters on the errors, we need to consider  $\partial E/\partial a^{\phi,l}$  and  $\partial E/\partial b^{\phi,l}$  in the subsampling layer l. Using Equation 2.29 and applying the chain rule yields the following:

$$\frac{\partial E}{\partial a^{\phi,l}} = \sum_{i,j} \frac{\partial E}{\partial y_{i,j}^{\phi,l}} \cdot \frac{\partial y_{i,j}^{\phi,l}}{\partial a^{\phi,l}} = \sum_{i,j} \frac{\partial E}{\partial y_{i,j}^{\phi,l}} \cdot f'(a^{\phi,l} \cdot \xi_{i,j}^{\phi,l} + b^{\phi,l}) \cdot \xi_{i,j}^{\phi,l}$$

(2.30)

$$\frac{\partial E}{\partial b^{\phi,l}} = \sum_{i,j} \frac{\partial E}{\partial y_{i,j}^{\phi,l}} \cdot \frac{\partial y_{i,j}^{\phi,l}}{\partial b^{\phi,l}} = \sum_{i,j} \frac{\partial E}{\partial y_{i,j}^{\phi,l}} \cdot f'(a^{\phi,l} \cdot \xi_{i,j}^{\phi,l} + b^{\phi,l})$$

(2.31)

The partial derivative  $\partial E/\partial y_{i',j'}^{\phi',l-1}$  in the above equations is still unknown. It expresses how the output of the layer l-1 influences the error. Let  $\phi$  denote the respective feature map in the layer l, and  $\phi'$  the corresponding feature map producing the input for  $\phi$ . Note that  $\phi'$  can only represent one single feature map, because  $\phi$  is a subsampling map. The chain rule can be leveraged here again:

$$\frac{\partial E}{\partial y_{i',j'}^{\phi',l-1}} = \sum_{i,j} \frac{\partial E}{\partial y_{i,j}^{\phi,l}} \cdot \frac{\partial y_{i,j}^{\phi,l}}{\partial \xi_{i,j}^{\phi,l}} \cdot \frac{\partial \xi_{i,j}^{\phi,l}}{\partial y_{i',j'}^{\phi',l-1}}$$

(2.32)

The derivative  $\partial E/\partial y_{i,j}^{\phi,l}$  is known by assumption. The expression  $\partial y_{i,j}^{\phi,l}/\partial \xi_{i,j}^{\phi,l}$  can be derived from Equation 2.29:

$$\frac{\partial y_{i,j}^{\phi,l}}{\partial \xi_{i,j}^{\phi,l}} = f'(a^{\phi,l} \cdot \xi_{i,j}^{\phi,l} + b^{\phi,l}) \cdot a^{\phi,l}$$

$$(2.33)$$

The evaluation of the last term from Equation 2.32 depends on the subsampling type. As mentioned before, we will be considering the average or maximum value.

Averaging yields:

$$\frac{\partial \xi_{i,j}^{\phi,l}}{\partial y_{i',j'}^{\phi',l-1}} = \frac{1}{r_x^l \cdot r_y^l} \tag{2.34}$$

Maximization yields:

$$\frac{\partial \xi_{i,j}^{\phi,l}}{\partial y_{i',j'}^{\phi',l-1}} = \begin{cases} 1 & \text{if } y_{i',j'}^{\phi',l-1} \text{ is the maximum value} \\ 0 & \text{otherwise} \end{cases}$$

(2.35)

We are now able to compute the error gradients for both trainable parameters  $a^{\phi,l}$  and  $b^{\phi,l}$ . However, the formal description of the Backpropagation algorithm from Section 2.2.2 needs to be adjusted, as it computes adjustment for weights  $\Delta w_{i,j}$  in fully-connected layer. In case of a subsampling layer, it needs to compute the adjustment of the trainable parameters  $\Delta a^{\phi,l}$  and  $\Delta b^{\phi,l}$ .

$$\Delta a^{\phi,l} = -\eta \frac{\partial E}{\partial a^{\phi,l}} \tag{2.36}$$

$$\Delta b^{\phi,l} = -\eta \frac{\partial E}{\partial b^{\phi,l}} \tag{2.37}$$

At this point we are able to propagate the error down towards the input layer using Equation 2.32, and adjust the trainable parameters using Equation 2.36 and Equation 2.37.

#### 2.3.4.2 Backpropagation in convolutional layer

In the case of convolutional layer, the only trainable parameters are the weights shared for neurons in the same feature map. Note that there is no activation function used in convolutional layers.

Let us discuss how the weights affect the error by computing the derivative  $\partial E/\partial w_{i,j}^{\phi,\phi',l}$  for the preceding convolutional layer l, feature map  $\phi$ , and the respective feature map  $\phi'$  in the layer l-1. This derivative can be computed using the chain rule and Equation 2.23. The expression  $\partial E/\partial y_{p,q}^{\phi,l}$  is assumed to be known.

$$\frac{\partial E}{\partial w_{i,j}^{\phi,\phi',l}} = \sum_{p=0}^{m_l-1} \sum_{q=0}^{n_l-1} \frac{\partial E}{\partial y_{p,q}^{\phi,l}} \cdot \frac{\partial y_{p,q}^{\phi,l}}{\partial w_{i,j}^{\phi,\phi',l}} = \sum_{p=0}^{m_l-1} \sum_{q=0}^{n_l-1} \frac{\partial E}{\partial y_{p,q}^{\phi,l}} \cdot y_{p+i,q+j}^{\phi',l-1}$$

(2.38)

The last derivative we need to know to be able to backpropagate the errors is  $\partial E/\partial y_{p,q}^{\phi',l-1}$ . To compute it, we need to consider the set of neurons in layer l connected to the output  $y_{p,q}^{\phi',l-1}$ . Let us denote this set  $\Theta_{p,q}^{\phi',l-1}$ . Let us further denote the output of neuron  $n \in \Theta_{p,q}^{\phi',l-1}$  with  $y_n$ , and denote the weight which connects neuron  $(p,q,\phi',l-1)$  to neuron n with  $w_n$ . Then we can apply the chain rule to obtain:

$$\frac{\partial E}{\partial y_{p,q}^{\phi',l-1}} = \sum_{n \in \Theta_{p,q}^{\phi',l-1}} \frac{\partial E}{\partial y_n} \cdot \frac{\partial y_n}{\partial y_{p,q}^{\phi',l-1}} = \sum_{n \in \Theta_{p,q}^{\phi',l-1}} \frac{\partial E}{\partial y_n} \cdot w_n \tag{2.39}$$

Since we know all the outputs  $y_{i,j}^{\phi,l}$  in layer l, and  $y_n \in \bigcup_{\phi,i,j} y_{i,j}^{\phi,l}$ , the derivative  $\partial E/\partial y_n$  is also assumed to be known.

# 2.4 Deep belief networks

The first description modeling a Deep Belief Network (DBN) was published in 1986 by Smolensky [32]. At the time, the model was referred to as "harmonium". It is a type of deep neural network composed of multiple layers, each layer consisting of visible neurons representing the layer input, and hidden neurons representing the layer output. In this text we will consider a layer to own the hidden neurons. The visible neurons will be owned by the preceding layer, for which these neurons are hidden. The visible neurons are fully interconnected with the hidden ones. The distinctive feature of a DBN is that there are no connections between the visible neurons, and no connections between the hidden neurons. The connections are symmetric, and are exclusively between the visible neurons and the hidden ones.

In the following text we will start with a definition of a stochastic neuron, which will be used in the DBNs. Then we will describe the architecture of Restricted Boltzmann Machines, which represent the main building block of DBNs. The following sections will explain the network's architecture and the training process.

#### 2.4.1 Stochastic model of a neuron

The model of a standard neuron depicted in Figure 2.2 is deterministic in a sense that its output is exactly defined for a given input. On the other hand the output of a stochastic neuron used in Boltzmann networks is probabilistic. The output y is binary, given by the probability  $P(\xi)$ .

$$y = \begin{cases} 1 & \text{with probability of } P(\xi) \\ 0 & \text{with probability of } 1 - P(\xi) \end{cases}$$

(2.40)

The probability function used here is again the sigmoid-shaped function:

$$P(\xi) = \frac{1}{1 + e^{-\frac{\xi}{T}}},\tag{2.41}$$

where T > 0 is the so-called *pseudotemperature* parameter used to control the level of noise in the probability. The *pseudotemperature* T may be thought of as a parameter representing the effect of thermal fluctuations in the neural synapses

causing noise in the signal being transferred. Note that as T approaches 0, this stochastic model becomes deterministic:

$$\lim_{T \to 0^{+}} P(\xi) = \lim_{T \to 0^{+}} \frac{1}{1 + e^{-\frac{\xi}{T}}} = \begin{cases} 1 & \text{for } \xi > 0\\ \frac{1}{2} & \text{for } \xi = 0\\ 0 & \text{for } \xi < 0 \end{cases}$$

(2.42)

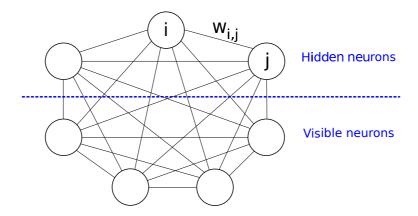

#### 2.4.2 Boltzmann machine

The Boltzmann machine is a stochastic neural network consisting of stochastic neurons first introduced by Hinton et al. [9]. It is referred to as a recurrent network, because all its connections are bidirectional, and there is a connection between every pair of neurons, even within the same layer. Therefore the graph of a Boltzmann network is always fully connected, as illustrated in Figure 2.10.

Let  $w_{i,j}$  be the weight of the connection between neuron i and j, then the following invariants hold true:

$$\forall i \neq j : w_{i,i} = 0$$

$$w_{i,j} = w_{j,i}$$

$$w_{i,j} \geq 0$$

$$(2.43)$$

The weights are often represented as a matrix W with zeros on the diagonal. Each neuron is binary and therefore can be either in 'on' or 'off' state, which is represented by boolean truth values  $s_i \in \{0,1\}$ . We will again denote the bias of the neuron i as  $\theta_i$ .

The neurons are partitioned into two functional groups: the so-called visible and hidden neurons. The visible neurons provide an interface between the network and its environment. The inputs are given as binary vectors. The hidden neurons on the other hand are trained to represent underlying constraints contained in the input vectors. In the following text, we will assume a sequential numbering of neurons in the network. For a network with n neurons in total and m visible neurons, the visible neurons will be numbered  $(1, \ldots, m)$ , and the hidden neurons  $(m+1, \ldots, n)$ . Having m visible neurons and an m-dimensional input vector  $\vec{v}$ , the visible neurons can be initialized to the corresponding elements of  $\vec{v}$ , where  $\forall i \in (1, \ldots, m) : s_i = v_i$ .

The primary goal of a Boltzmann network is to correctly model input patterns according to Boltzmann distribution. The network can thus perform pattern reconstruction. Specifically, provided the network has learned the underlying model correctly, when presented only partial input pattern, it can complete the missing values by computing the missing states of the visible neurons.

A good approach to assessing the performance of a network is to define a measure for evaluating how its internal parameters and structure represent the internal constraints in the input data. Such a measure can then be addressed as a typical best-fit problem, solved by iterative attempts to decrease the value of this measure, until reaching (perhaps the global) minimum. As Hopfield showed in his research [17], energy can be well used as such measure, and is analogously defined in the context of Boltzmann machines. The energy of Boltzmann machine for a configuration of neuron states s can be defined as:

Figure 2.10: An illustration of a Boltzmann Machine with 3 hidden neurons and 4 visible neurons.

$$E(s) = -\sum_{i < j} w_{i,j} s_i s_j - \sum_i \theta_i s_i.$$

(2.44)

where  $s_i$  are the binary states of neurons,  $w_{i,j}$  are the weights between them, and  $\theta_i$  are their biases. The impact of a single unit's state  $s_i$  on global energy can then be computed simply by

$$\Delta E(s_i) = \sum_j w_{ij} s_j + \theta_i \tag{2.45}$$

The energy can be used in the training process using gradient descend method to find the lowest possible energy of the system for the given input.

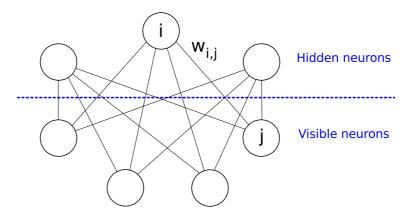

#### 2.4.3 Restricted Boltzmann Machine

Equation 2.45 suggests an iterative training, where the energy differential  $\Delta E$  for each state  $s_i$  must be computed sequentially. The root cause are the interconnections between the visible and hidden neurons, which make the neuron states dependent on each other. The Restricted Boltzmann Machine (RBM) parallelizes this process by removing these connections, creating a bipartite graph between visible and hidden neurons (see Figure 2.11).

Figure 2.11: An illustration of a Restricted Boltzmann Machine with 3 hidden neurons and 4 visible neurons.

Eliminating these connections results into new energy definitions for a joint configuration of visible and hidden neurons (v, h):

$$E(\vec{v}, \vec{h}) = -\sum_{(i,j)} w_{i,j} v_i h_j - \sum_i a_i v_i - \sum_j b_j h_j.$$

(2.46)

$$\Delta E(v_i, \vec{h}) = \sum_j w_{ij} h_j + a_i \tag{2.47}$$

$$\Delta E(\vec{v}, h_j) = \sum_i w_{ij} v_i + b_j \tag{2.48}$$

where  $v_i$ ,  $h_j$  are the binary states of the visible unit i and the hidden unit j,  $a_i$ ,  $b_j$  are their biases, and  $w_{i,j}$  is the weight between them. Unlike in the case of the standard Boltzmann Machine (Eq. 2.45), the Restricted Boltzmann Machine does not depend on visible or hidden neurons when computing the energy differential for the visible or hidden neuron, respectively (Eq. 2.47 and 2.48). For this reason we will be using this model and take advantage of its parallelization potential in our implementation.

#### 2.4.4 Training Restricted Boltzmann Machines

RBMs are trained using unsupervised learning. They are not performing classification themselves, but instead they are able to learn to reconstruct data in an unsupervised fashion. Let us assume we have some training set V, a matrix where each row represents the input visible vector  $\vec{v}$ . The further text in this section we will be inspired by Hinton's Practical guide to training RBMs [14].

RBMs learn by encoding the probability distribution of the input data into the weight parameters. The purpose of training is to maximize the product of probabilities assigned to the training patterns from V, thus we are looking for weight assignment  $W_m$  producing the maximal probability:

$$W_m = \max_{W} \prod_{\vec{v} \in V} p(\vec{v}) \tag{2.49}$$

The RBM assigns a probability to every possible pair of a visible and hidden vector via the energy function defined in Equation 2.46:

$$p(\vec{v}, \vec{h}) = \frac{1}{Z} e^{-E(\vec{v}, \vec{h})}$$

(2.50)

where Z is the so-called partition function defined by summing over the energy of all possible neuron states:

$$Z = \sum_{\vec{v}\,\vec{h}} e^{-E(\vec{v},\vec{h})} \tag{2.51}$$

The probability RBM assigns to a visible vector  $\vec{v}$  is then defined by summing over all possible hidden states:

$$p(\vec{v}) = \frac{1}{Z} \sum_{\vec{k}} e^{-E(\vec{v}, \vec{h})}$$

(2.52)

The probability assigned to a visible vector (i.e. input pattern) can be effectively raised by adjusting the weights and bias to lower the energy of that vector, and to raise the energy of other visible vectors. To determine the desirable weight adjustment we need the derivative of the probability with respect to the adjusted weight, which becomes surprisingly simple for the log probability:

$$\frac{\partial \log p(\vec{v})}{\partial w_{i,j}} = \langle v_i h_j \rangle_{data} - \langle v_i h_j \rangle_{model}$$

(2.53)

where the notation  $\langle \rangle$  denotes the expectations under the distribution specified by the training data and the model respectively. From the above equation we can directly deduce the rule for performing stochastic steepest ascent in the log probability of the training data:

$$\Delta w_{i,j} = \eta \left( \langle v_i h_j \rangle_{data} - \langle v_i h_j \rangle_{model} \right) \tag{2.54}$$

where  $\eta > 0$  is the learning rate.

The expectations under the distribution specified by the training data can be obtained easily by sampling the hidden neuron states from the visible ones. Given a training input pattern  $\vec{v}$ , the probability of the binary state  $h_i$  being 1 (the "on" state) is:

$$p(h_j = 1|\vec{v}) = \sigma(b_j + \sum_i v_i w_{i,j})$$

(2.55)

where  $\sigma$  is the activation function. The most commonly used activation function is sigmoid (Eq. 2.2). After sampling the hidden state,  $v_i h_j$  represents the expectation under the data distribution in equation 2.54.

$$p(v_i = 1|\vec{h}) = \sigma(a_i + \sum_{j} h_j w_{i,j})$$

(2.56)

The sampling of the expectations under the distribution specified by the model is much more difficult to obtain. It can be done by randomly initializing the visible states and performing sampling back and forth using Eq. 2.55 and Eq. 2.56. Since the initial visible states are random, it takes a very long time until the RBM converges to the model distribution.

#### 2.4.4.1 Contrastive Divergence

Instead of randomly initializing the visible states, a much more effective approach is used in the constrastive divergence (CD) learning procedure first introduced by Hinton [15]. Note that for readability reasons, we will be labeling the visible vector with v and hidden vector with v, instead of  $\vec{v}$  and  $\vec{h}$ . Since we eventually expect  $p_{data}(v) \approx p_{model}(v)$ , we can initialize the visible states with input data, and reconstruct the model expectations from them. This results in a much faster convergence to the model distribution. The CD algorithm can be summarized by the below steps, which are iterated over each sample in the training dataset:

1. Pick training sample v and clamp it onto the visible neurons (binary input is assumed).

- 2. Compute the probabilities of hidden neurons  $p_h$  by multiplying the visible vector v with the weights matrix W as  $p_h = \sigma(v \cdot W)$  (see Eq. 2.55).

- 3. Sample the hidden states h from the probabilities  $p_h$ .

- 4. Compute the outer product of vectors v and  $p_h$ , let us call it positive gradient  $\phi^+ = v \cdot p_h^T$ .

- 5. Sample a reconstruction of the visible states v' from the hidden states h (see Eq. 2.56). Then resample the hidden states h' from the reconstruction of the visible states v'. (Gibbs sampling step)

- 6. Compute the outer product of v' and h', let us call it negative gradient  $\phi^- = v' \cdot h'^T$ .

- 7. Compute the weight updates as the positive gradient minus the negative gradient:  $\Delta W = \eta (\phi^+ \phi^-)$ .

- 8. Update the weights with new values:  $w'_{i,j} = w_{i,j} + \Delta w_{i,j}$ .

The Gibbs sampling step can be repeated multiple times to converge closer to the model distribution. The number of repetitions is often included in the abbreviation of the algorithm, where for k repetitions the algorithm is referred to as CD-k [15, 14]. Experiments reported so far show, that CD-1 is already producing very decent results [5].

#### 2.4.4.2 Persistent Contrastive Divergence

At present, constrastive divergence is one of the most popular gradient approximations for RBMs. However, there are multiple alterations to the standard CD algorithm, and it is not obvious which is the best one. A very common alternation is Persistent CD, abbreviated as PCD. Some research claims that PCD produces more meaningful feature detectors, and outperforms the other variants of CD algorithms [35].

PCD algorithm uses a different approximation for sampling states than CD. It eliminates Step 3 when compared to standard CD described in the above steps. This step initializes the hidden states based on the input pattern. As a result, the sampling chain is being restarted for every observed pattern. Instead, PCD initializes the hidden states only once at the beginning of the training. This causes the single chain of sampling throughout the whole training, which helps move faster towards the model distribution  $p_{model}$  rather then  $p_{data}$ . The smaller the learning rate, the better PCD works [35]. It is because the smaller parameter updates are then small enough compared to changes in the sampling chain (mixing rate of Markov chain), and the chain can easier catch up to the changes in the model.

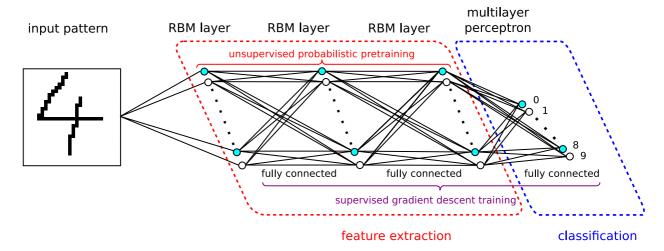

## 2.4.5 Architecture of a Deep Belief Network

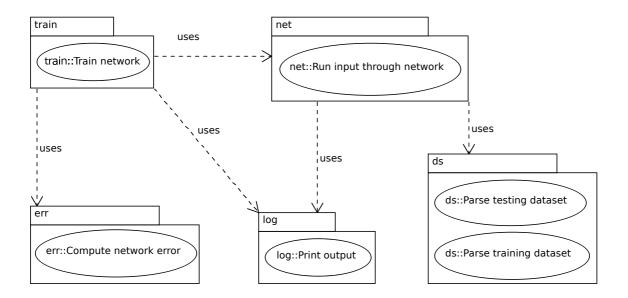

The Restricted Boltzmann Machines themselves are capable of detecting and extracting features from input data. Several layers of RBMs can be stacked one onto each other to form a multilayer network [16]. Each RBM layer uses

the hidden neurons from preceding RBM layer as its input (see Figure 2.12). The deep architecture with multiple layers can then extract deep hierarchical representation of the training data.

Figure 2.12: Architecture of a Deep Belief Network.

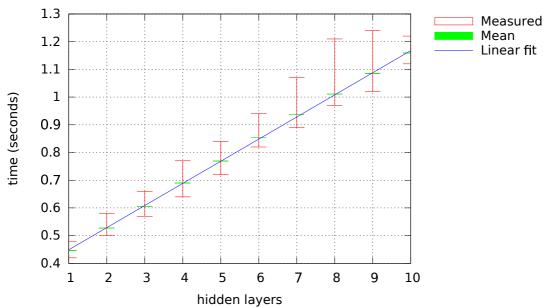

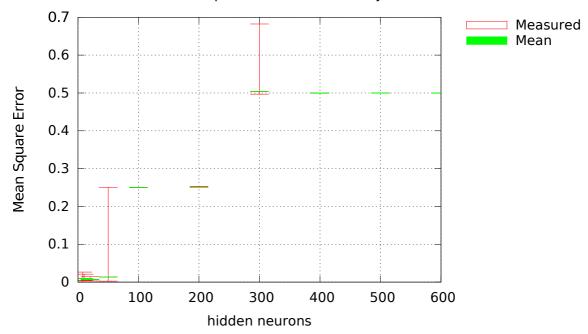

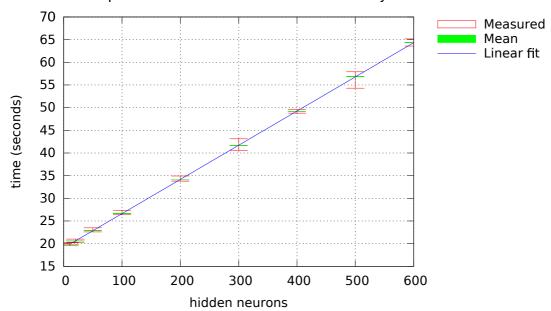

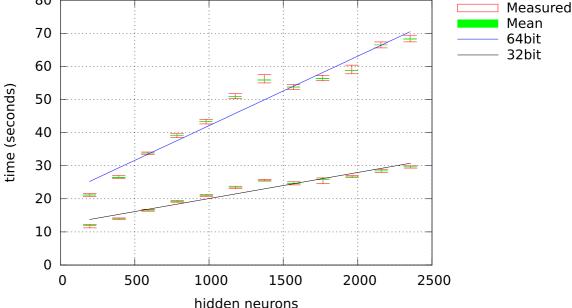

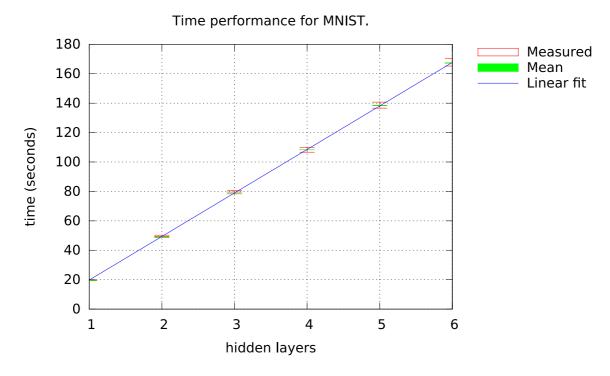

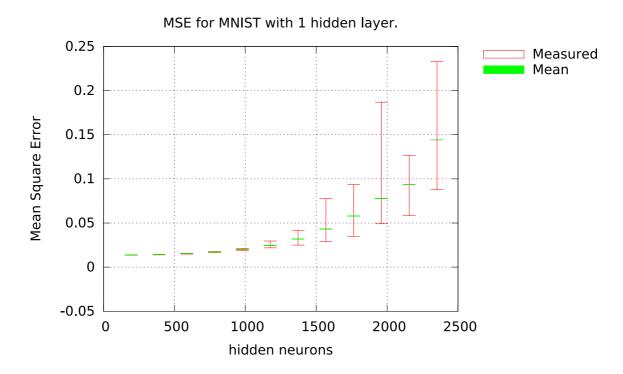

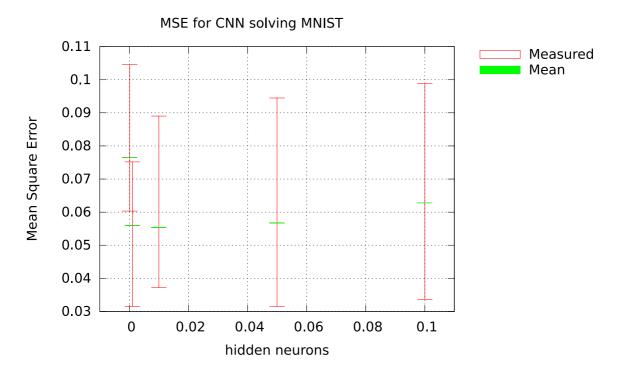

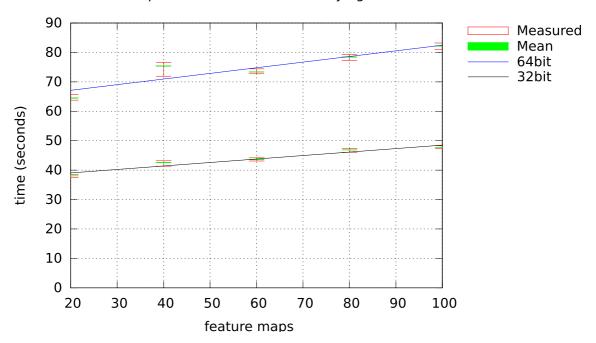

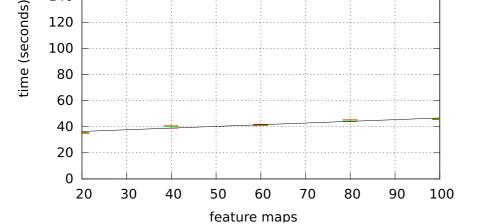

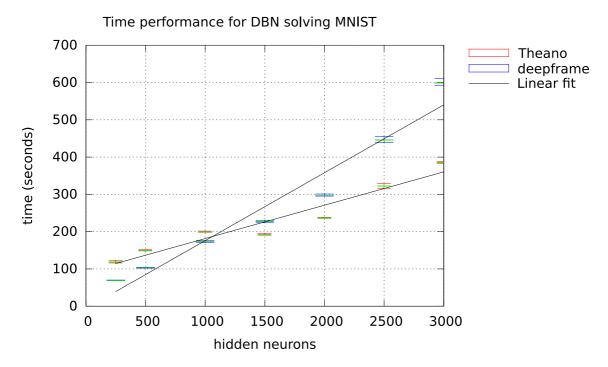

A set of RBM layers performs the feature detection task, while the classification task is performed by using a multilayer perceptron as the last layer. The last MLP layer is again using the hidden neurons of the preceding RBM layer as its input. The resulting architecture is a mixture of probabilistic neurons in the feature extraction phase, and deterministric neurons in the classification phase.