Charles University in Prague Faculty of Mathematics and Physics

DOCTORAL THESIS

# RNDr. Martin Kruliš

# Employing Parallel Architectures in Similarity Search

Departement of Software Engineering

Supervisor of the doctoral thesis: RNDr. Jakub Yaghob, Ph.D.

Study programme: 4I2, Software Systems

Prague, 2013

I would like to give thanks to many people who helped me carry out this thesis. First of all, I would like to thank my advisor RNDr. Jakub Yaghob, Ph.D., who led me kindly through the dangerous realms of parallel programming, who solved many of my technical problems, and who encouraged me in my work.

I would like to thank my family and my fiancée Háňa for their love, patience, and understanding. They have been a great support and they provided a moral courage in the times of need.

Finally, I would like to thank my friends and coworkers for their advice and technical help they gave me on countless occasions. Especially, I give my thanks to Katie for the language and grammar corrections of the thesis, to Zbyněk Falt for the assistance with the experiments on the Bobox system, and to Jakub Lokoč for his insights into the dark arts of the similarity search.

I declare that I carried out this doctoral thesis independently, and only with the cited sources, literature and other professional sources.

I understand that my work relates to the rights and obligations under the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular the fact that the Charles University in Prague has the right to conclude a license agreement on the use of this work as a school work pursuant to Section 60 paragraph 1 of the Copyright Act.

18th March 2013 in Prague

RNDr. Martin Kruliš

Název práce: Nasazení paralelních architektur v podobnostním vyhledávání

Autor: RNDr. Martin Kruliš

Katedra: Katedra Softwarového Inženýrství

Vedoucí disertační práce: RNDr. Jakub Yaghob, Ph.D.

Abstrakt: Tato práce se zabývá možnostmi nasazení masivně paralelních architektur v databázových systémech využívajících podobnostní vyhledávání. Hlavním předmětem našeho zájmu je využití výpočetní síly současné generace grafických karet pro vyhledávání v databázích obrázků. I přes významný pokrok v posledních letech zůstává oblast podobnostního vyhledávání velmi výpočetně náročná, takže je možné tyto metody aplikovat pouze u databází menšího rozsahu. Grafické čipy disponují obrovskou výpočetní silou, avšak jejich použitelnost pro konkrétní problémy bývá komplikovaná z důvodu specifických vlastností této architektury, které si vyžadují individuální úpravu existujících algoritmů a datových struktur. Zabývali jsme se všemi aspekty této problematiky, od efektivního využití grafických čipů pro obecné výpočty přes akceleraci vyhledávacího procesu až po efektivní indexaci obrázků. Ve většině případů přineslo nasazení grafických karet zrychlení přibližně o dva řády ve srovnání s jednojádrovými procesory a několikanásobné zrychlení ve srovnání s běžnými víceprocesorovými NUMA servery. Tato práce shrnuje naše poznatky z několikaletého výzkumu, algoritmy upravené pro specifické podmínky masivně paralelních čipů, ale také výsledky provedených experimentů, které potvrzují naše závěry.

Klíčová slova: paralelní, databáze, plánování, GPGPU, podobnostní vyhledávání

Title: Employing Parallel Architectures in Similarity Search

Author: RNDr. Martin Kruliš

Department: Departement of Software Engineering

Supervisor: RNDr. Jakub Yaghob, Ph.D.

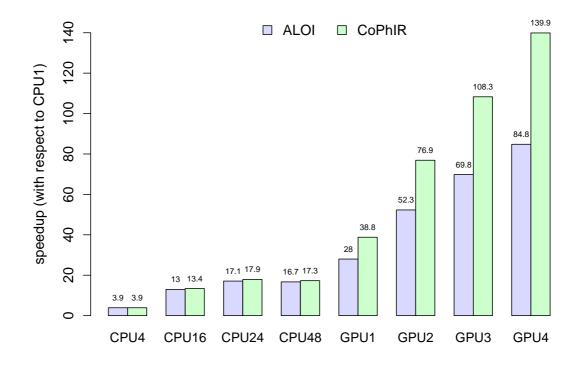

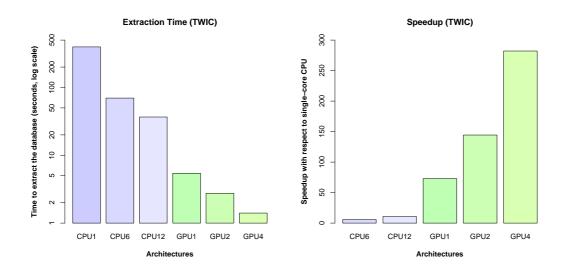

Abstract: This work examines the possibilities of employing highly parallel architectures in database systems, which are based on the similarity search paradigm. The main objective of our research is utilizing the computational power of current GPU devices for similarity search in the databases of images. Despite leaping progress made in the past few years, the similarity search problems remain very expensive from a computational point of view, which limits the scope of their applicability. GPU devices have a tremendous computational power at their disposal; however, the usability of this power for particular problems is often complicated due to the specific properties of this architecture. Therefore, the existing algorithms and data structures require extensive modifications if they are to be adapted for the GPUs. We have addressed all the aspects of this domain, such as efficient utilization of the GPU hardware for generic computations, parallelization of similarity search process, and acceleration of image indexing techniques. In most cases, employing the GPU devices brought a speedup of two orders of magnitude with respect to single-core CPUs and approximately one order of magnitude with respect to multiprocessor NUMA servers. This thesis summarizes our experience and discoveries from several years of research, related algorithms adopted for the specific conditions of GPU architectures, and the results of empirical experiments performed in order to verify our claims.

Keywords: parallel, databases, scheduling, GPGPU, similarity search

# Contents

| 1        | 1 Introduction |                                                                                                                                           |  |  |  |  |  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | 1.1            | Embracing Parallelism                                                                                                                     |  |  |  |  |  |

|          | 1.2            | Outlining Objectives                                                                                                                      |  |  |  |  |  |

|          | 1.3            | Contributions                                                                                                                             |  |  |  |  |  |

| 0        | ъ              | allel Architectures 7                                                                                                                     |  |  |  |  |  |

| <b>2</b> | Par<br>2.1     |                                                                                                                                           |  |  |  |  |  |

|          | 2.1            | Multi-Core CPUs       7         2.1.1       Parallelism in CPUs       7                                                                   |  |  |  |  |  |

|          |                |                                                                                                                                           |  |  |  |  |  |

|          |                | 2.1.2 Memory Issues $\dots \dots \dots$   |  |  |  |  |  |

|          | 0.0            | 2.1.3 API and Parallel Libraries                                                                                                          |  |  |  |  |  |

|          | 2.2            | Many-Core GPUs                                                                                                                            |  |  |  |  |  |

|          |                | 2.2.1 Hardware Overview                                                                                                                   |  |  |  |  |  |

|          |                | 2.2.2 Execution Model $\dots \dots \dots$ |  |  |  |  |  |

|          |                | 2.2.3 Memory Structure                                                                                                                    |  |  |  |  |  |

|          |                | 2.2.4 Memory Performance Issues                                                                                                           |  |  |  |  |  |

|          |                | 2.2.5 GPU Programming                                                                                                                     |  |  |  |  |  |

| 3        | Tas            | Task Scheduling 25                                                                                                                        |  |  |  |  |  |

|          | 3.1            | The Problem of Scheduling                                                                                                                 |  |  |  |  |  |

|          | 3.2            | Related Work                                                                                                                              |  |  |  |  |  |

|          | -              | 3.2.1 Task Scheduling                                                                                                                     |  |  |  |  |  |

|          |                | 3.2.2 Intel Threading Building Blocks Scheduler                                                                                           |  |  |  |  |  |

|          |                | 3.2.3 The Bobox System                                                                                                                    |  |  |  |  |  |

|          | 3.3            | Blocking Tasks                                                                                                                            |  |  |  |  |  |

|          | 0.0            | 3.3.1 Naïve Solutions                                                                                                                     |  |  |  |  |  |

|          |                | 3.3.2 The Bobox Solution                                                                                                                  |  |  |  |  |  |

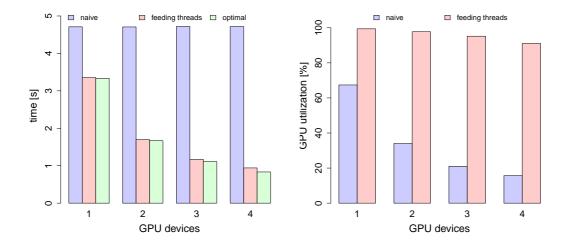

|          | 3.4            | Hybrid CPU-GPU Scheduling                                                                                                                 |  |  |  |  |  |

|          | 0.1            | 3.4.1 OpenCL Framework                                                                                                                    |  |  |  |  |  |

|          |                | 3.4.2 Model Case Study                                                                                                                    |  |  |  |  |  |

|          |                | 3.4.3 Framework Design                                                                                                                    |  |  |  |  |  |

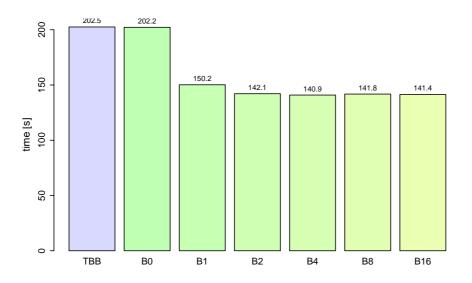

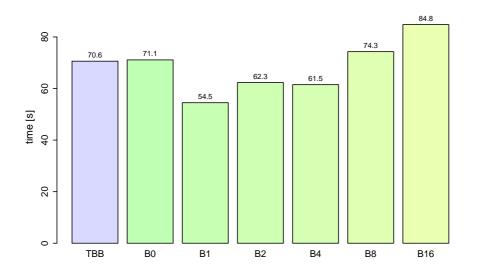

|          | 3.5            | Experimental Evaluation                                                                                                                   |  |  |  |  |  |

|          | 0.0            | 3.5.1 Hardware and Methodology                                                                                                            |  |  |  |  |  |

|          |                | 3.5.2 Blocking Tasks                                                                                                                      |  |  |  |  |  |

|          |                | 3.5.3 Hybrid Scheduling 49                                                                                                                |  |  |  |  |  |

|          |                |                                                                                                                                           |  |  |  |  |  |

| 4        |                | ccelerating Similarity Search 51                                                                                                          |  |  |  |  |  |

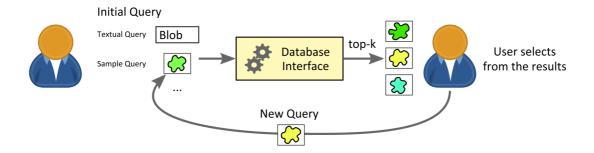

|          | 4.1            | Introduction                                                                                                                              |  |  |  |  |  |

|          |                | 4.1.1 Content-based Retrieval                                                                                                             |  |  |  |  |  |

|          |                | 4.1.2 Object Descriptors                                                                                                                  |  |  |  |  |  |

|          |                | 4.1.3 Distance Functions                                                                                                                  |  |  |  |  |  |

|          |                | 4.1.4 Signature Quadratic Form Distance                                                                                                   |  |  |  |  |  |

|          | 4.2            | Indexing                                                                                                                                  |  |  |  |  |  |

|          |                | $4.2.1  \text{Metric Spaces}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                            |  |  |  |  |  |

|          |                | $4.2.2  \text{Pivots}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   |  |  |  |  |  |

|          |                | 4.2.3 List of Clusters                                                                                                                    |  |  |  |  |  |

| $\mathbf{A}$   | Attached Digital Content 13 |                |                                                                   |       |  |  |

|----------------|-----------------------------|----------------|-------------------------------------------------------------------|-------|--|--|

| Conclusion 135 |                             |                |                                                                   |       |  |  |

|                |                             | 5.4.3          | Traversing the Parameter Space                                    | . 129 |  |  |

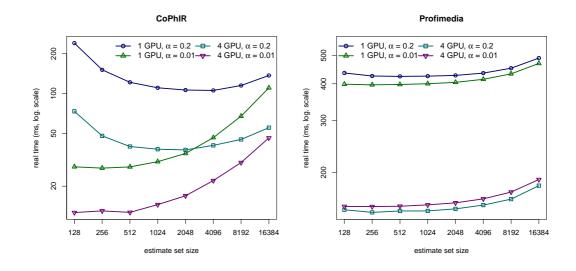

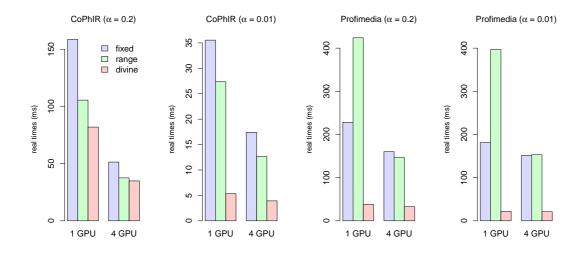

|                |                             | 5.4.2          | Performance Evaluation                                            |       |  |  |

|                |                             | 5.4.1          | Hardware and Methodology                                          |       |  |  |

|                | 5.4                         | Exper          | $\dot{m}$ ents                                                    |       |  |  |

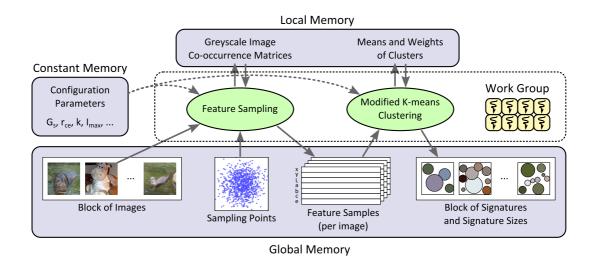

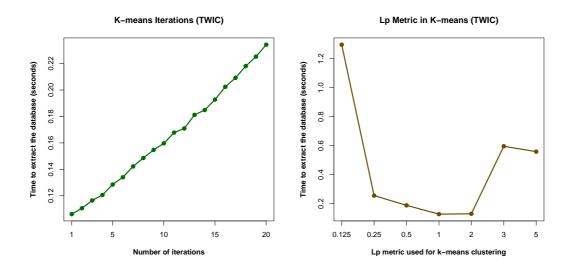

|                |                             | 5.3.4          | K-means Clustering                                                | . 120 |  |  |

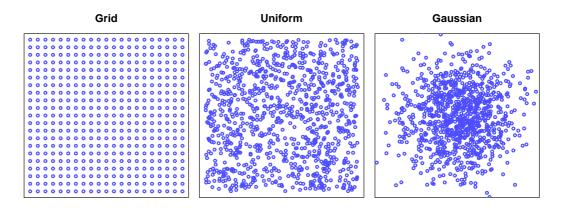

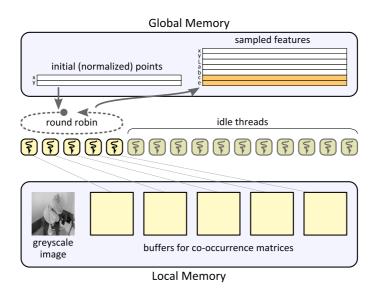

|                |                             | 5.3.3          | Sampling Features                                                 |       |  |  |

|                |                             | 5.3.2          | The Design of the Extractor                                       | . 116 |  |  |

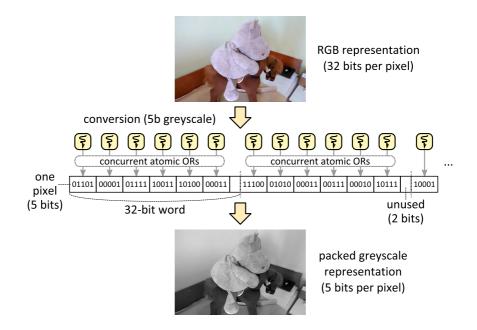

|                |                             | 5.3.1          | Problem Analysis                                                  | . 114 |  |  |

|                | 5.3                         | GPU            | Implementation                                                    | . 114 |  |  |

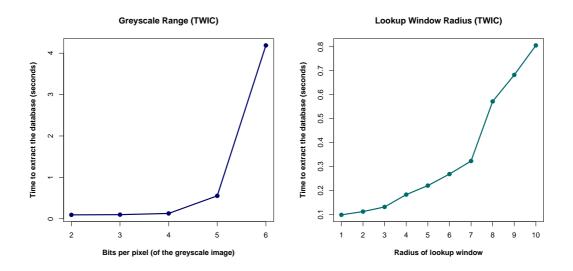

|                |                             | 5.2.4          | Extraction Parameters                                             | . 113 |  |  |

|                |                             | 5.2.3          | K-means Clustering                                                |       |  |  |

|                |                             | 5.2.2          | Sampling Features                                                 | . 106 |  |  |

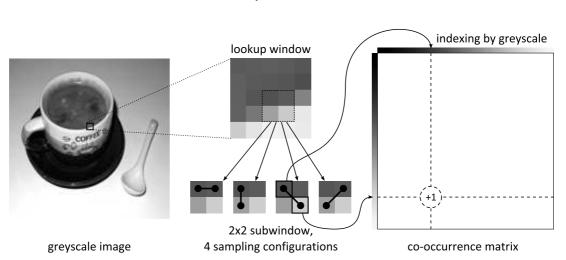

|                |                             | 5.2.1          | Extraction Overview                                               | . 105 |  |  |

|                | 5.2                         | The F          | Peature Extraction                                                | . 105 |  |  |

|                |                             | 5.1.2          | Related Work                                                      | . 104 |  |  |

|                |                             | 5.1.1          | Motivation                                                        | . 103 |  |  |

|                | 5.1                         | Introd         | luction                                                           | . 103 |  |  |

| <b>5</b>       | Image Feature Extraction    |                |                                                                   |       |  |  |

|                |                             | 4.7.4          | Parallel $k$ Nearest Neighbours with Prefiltering $\ldots \ldots$ | . 100 |  |  |

|                |                             | 4.7.3          | Metric and Ptolemaic Indexing                                     |       |  |  |

|                |                             | 4.7.2          | Parallel SQFD                                                     |       |  |  |

|                |                             | 4.7.1          | Hardware and Methodology                                          |       |  |  |

|                | 4.7                         | Exper          | $\dot{m}$ ents                                                    | . 92  |  |  |

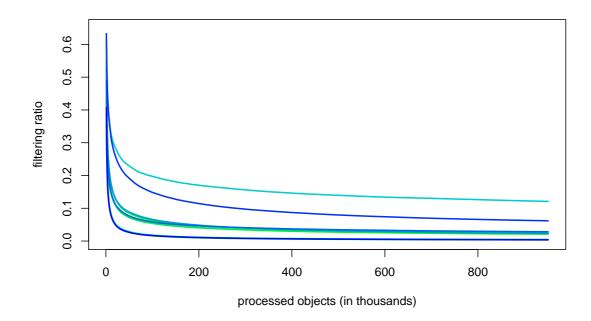

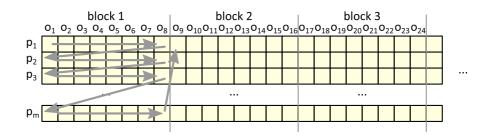

|                |                             | 4.6.2          | Range Estimation Algorithm                                        | . 90  |  |  |

|                |                             | 4.6.1          | Block Dispatching Strategies                                      | . 88  |  |  |

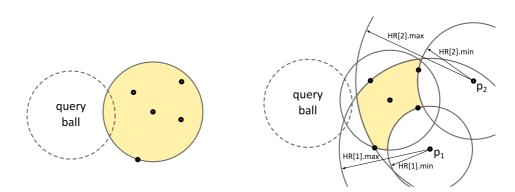

|                | 4.6                         | Prefilt        | tering for $k$ Nearest Neighbours $\ldots$                        |       |  |  |

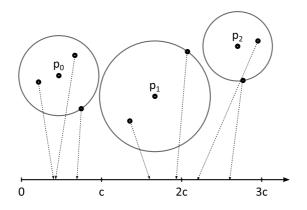

|                |                             | 4.5.2          | Precomputing Lower Bounds                                         |       |  |  |

|                | -                           | 4.5.1          | Problem Analysis                                                  |       |  |  |

|                | 4.5                         |                | lel Approach to Metric Indexing                                   |       |  |  |

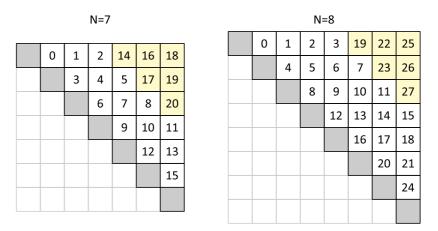

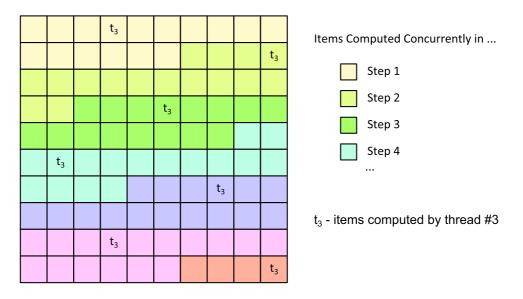

|                |                             | 4.4.3          | Parallel Implementation of SQFD                                   |       |  |  |

|                |                             | 4.4.2          | Similarity Search in Parallel Environment                         |       |  |  |

|                | 1.1                         | 4.4.1          | Problem Analysis                                                  |       |  |  |

|                | 4.4                         |                | erating SQFD by GPUs                                              |       |  |  |

|                | 4.3                         | -              | ed Work                                                           |       |  |  |

|                |                             | 4.2.5<br>4.2.6 | M-Index                                                           |       |  |  |

|                |                             | 4.2.4<br>4.2.5 | M-tree and PM-tree                                                |       |  |  |

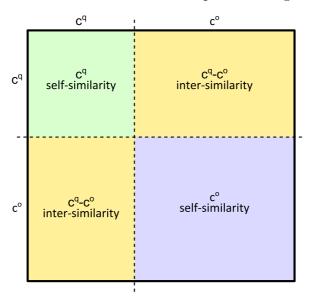

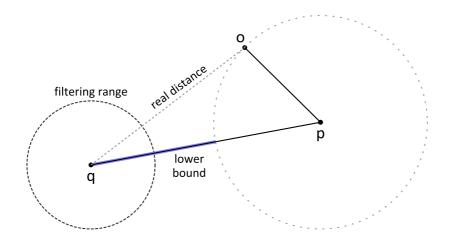

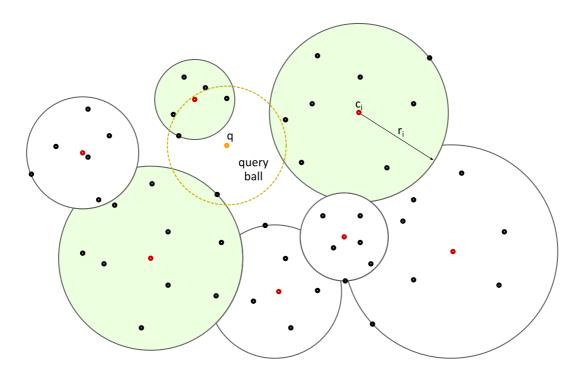

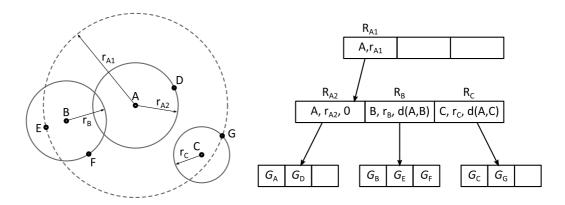

|                |                             | 4.2.4          | M tree and PM tree                                                | 67    |  |  |

# 1. Introduction

Software efficiency has been an intensively discussed issue since the very dawn of the computer science. Efficiency has been affecting many attributes of information systems, such as response times or the maximal size of the data we can process in a reasonable time. In the past, the performance of an application was determined mostly by the selection of appropriate algorithms and data structures, quality of the implementation, the compiler used, and the computational speed of the processor. The instruction processing speed was the leading factor since major improvements of most algorithms are quite rare and the optimal implementation is usually tailored to the compiler and the CPU architecture.

The computational speed of a processor was tightly linked to its operating frequency and the frequency corelated strongly with the number (and size) of the transistors on the chip. As the number of transistors has doubled every one or two years [1, 2], the performance of computers, and thus the software, was leaping steadily. Unfortunately, this trend reached an impasse at the beginning of the  $21^{st}$  century. It was discovered that the heat production of silicon-based chips is cubically proportional<sup>1</sup> to the frequency of the chip. Even though the cooling technologies have developed rapidly to match the needs of the CPUs, the frequency-boosting approach become unsustainable in the long run.

The frequency pursuit was abandoned and the CPU development ventured into the domain of multi-core parallelism. Current mainstream processors are equipped with multiple computational cores which are quite independent. They share only the die casing and a few resources such as the external busses, the memory controllers, or the L3 cache. Most of the Intel CPUs also employ the hyper-threading technology, which maps two virtual CPU cores to one physical, so the internal (and often redundant) units of the core can be better utilized. Furthermore, we can observe that the nonuniform memory architecture systems (NUMA), that encompass multiple physical processors (each managing its own part of the memory), are becoming increasingly popular. The combination of these factors has caused every up-to-date server to have tens of CPU cores, which all need to be utilized in order to achieve an optimal performance.

Another major hardware revolution happened in the field of graphical processing units. In 2006, the GPU stream processor architectures evolved to a point where the GPUs were capable of processing general computational tasks in addition to the traditional image operations and 3D graphic rendering. This generation of generic purpose GPUs gave us a highly parallel architecture capable of processing data at speeds that cannot be achieved even by the best multi-core CPUs. Graphical chips of the day contain from hundreds to thousands computational cores. Unfortunately, this architecture is bound with many limitations concerning the parallel execution model and the memory transfers, which restricts its applicability to rather specific data-parallel problems.

In addition to multi-core CPUs and many-core GPUs, other parallel platforms available for common PCs and servers have been introduced recently. For

<sup>&</sup>lt;sup>1</sup>Actually, the  $P = CV^2 f$ , where P is power, C is capacitance, V is voltage, and f is frequency [3]. According to frequency-voltage configuration tables, the V is approximately lineary dependent on f.

instance, the IBM Cell processors [4] or the Intel Many Integrated Core (MIC) architecture [5]. These platforms only prove that the trend of parallelization is quite strong in the current hardware and that we need to adapt our algorithms, implementation techniques, and programming paradigms in order to fully exploit their computational power.

## **1.1** Embracing Parallelism

It has been established that parallelism is one of the most essential things affecting the efficiency of current applications and there are many computational problems that can really benefit from a concurrent execution [6, 7, 8]. We would like to discuss a few very important issues that rise with the introduction of parallelism into algorithms before advancing further.

#### **Performance Evaluation**

As our work focuses on improving the performance of applications by embracing parallelism, we need to address the issue of performance evaluation. The theoretical approach, which operates with well established time complexities of algorithms, is not quite satisfactory in this case. On the other hand, the naïve approach of measuring the real execution time is highly dependent on various hardware factors and it suffers from significant errors of measurement. Unfortunately, the real running time is the only practical thing we can measure with acceptable relevance. In the light of these facts, we will provide most of the results as the *parallel speedup*, which is computed as

$$\text{Speedup} = \frac{t_{serial}}{t_{parallel}}$$

where  $t_{serial}$  is the real time required by the best serial version of the algorithm and  $t_{parallel}$  is the real time taken by the parallel version. Both versions are executed on the same data, thus solving exactly the same problem.

The speedup is always provided along with the number of cores (threads, devices, ...) used for the parallel version of the algorithm. We are trying to reduce the error of measurement by timing the serial and the parallel version of the algorithm on the same machine, using the same compiler, and under the same conditions. If we provide real times in our results, they should be perceived only as illustrational and the emphasis is on the speedup measured.

#### Scalability and Amdahl's Law

We usually measure the speedup in several different settings, when the parallel implementation utilizes a different number of cores. These tests are designed to asses the *scalability* of the algorithm. In other words, how many computational units can be efficiently utilized, or how well is the problem parallelable. In an optimal case, the speedup is equal to the number of computational units used (i.e.,  $2 \times$  on dual-core,  $4 \times$  on quad-core, etc.) and we denote this case the *linear speedup*. The scalability also helps us predict how the application will perform in

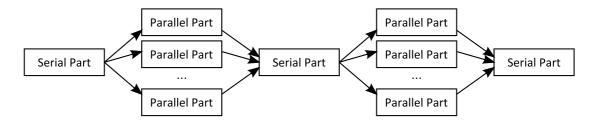

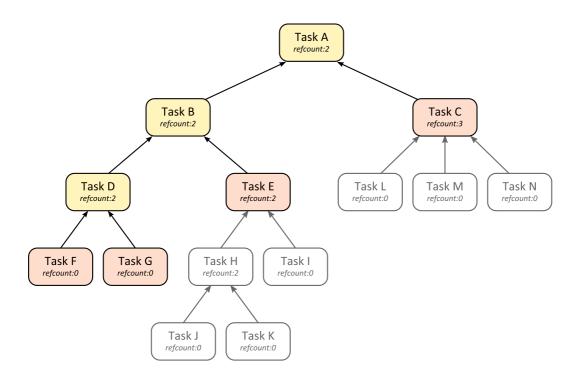

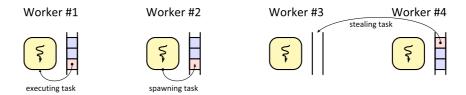

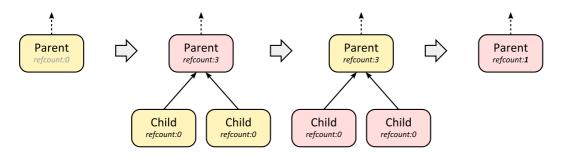

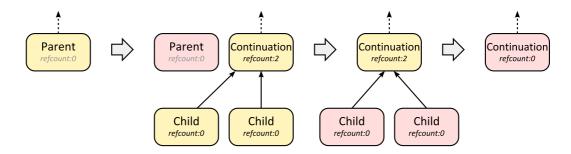

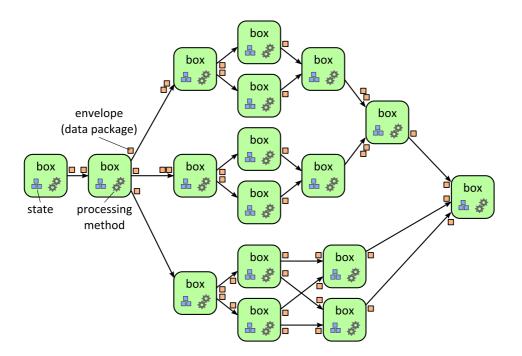

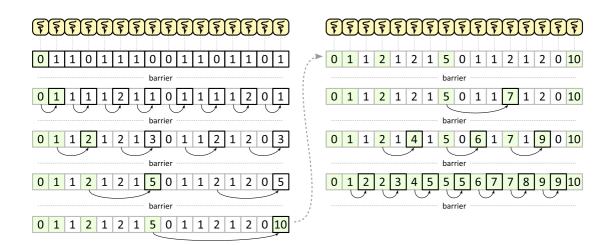

Figure 1.1: An example of the algorithm decomposition

the future as each new generation of CPUs and GPUs has more cores than the previous generation.

The scalability of an algorithm can also be determined by measuring the ratio of its serial and parallel parts (as depicted in Figure 1.1). If we identify the sizes of these parts, we can use the Amdahl's Law [9]

$$S_N = \frac{1}{(1-P) + \frac{P}{N}}$$

to estimate the speedup in advance. The  $S_N$  denotes speedup of the algorithm when N computational units are used and the P is the relative size of the parallel part of the algorithm. The speedup estimation becomes particularly interesting when the N tends to the infinity:

$$\lim_{N \to \infty} S_N = \lim_{N \to \infty} \frac{1}{(1 - P) + \frac{P}{N}} = \frac{1}{1 - P}$$

Even though this might sound excessively theoretic, it often helps us understand, what happens when an algorithm is moved from multi-core CPUs with tens of cores to a multi-GPU system with thousands of cores. For instance, if the serial part of the algorithm takes 5% of total work, we will never be able to achieve greater speedup than  $20\times$ , no matter how many cores we can employ. In such case, we can observe  $3.48\times$  speedup on a quad-core CPU (which looks adequate); however, we may achieve only  $19.3\times$  speedup on a 512-core GPU card<sup>2</sup>. Therefore, one of our main objectives is to reduce the serial parts as much as possible even at the cost of using an algorithm with suboptimal time complexity.

# 1.2 Outlining Objectives

This thesis focuses mainly on the problematics of database systems that employ similarity search and content-based retrieval. The main objective is to identify the key points that will benefit the most from parallelism and to exploit them to improve the performance of these systems. A particular emphasis was put on the utilization of generic purpose GPUs as they were the only highly parallel platform generally available at the time our research begun.

Current hardware architectures are quite complex. Understanding the design of these architectures is essential for developing an optimal parallel algorithms. Therefore, we dedicated Chapter 2 to revise the multi-core CPU and many-core GPU architectures of the day.

<sup>&</sup>lt;sup>2</sup>This example is only illustrational as we inadequately compare results of two platforms.

The first part of our research addresses the problems introduced by using a heterogeneous computational platform, where the operating systems and the main part of the application runs on a multi-core CPU(s), but computationally expensive parts are accelerated by the GPU devices. The task scheduling becomes more difficult as the GPU may wait for the CPU or vice versa. We have studied related problems and propose some solutions in Chapter 3.

The second and the most important part of the work is dedicated to the various problems of multimedia databases, especially the efficiency of contentbased retrieval and similarity search in large image databases. We have identified several algorithms that would benefit greatly from parallelism. These algorithms and their parallel modifications are described in Chapter 4.

Finally, we focus on the problem of feature extraction, which is used to create the image descriptors for the similarity search. Our main objective is to accelerate the extraction process, so we can index larger datasets in a feasible time and perform many experiments to tune the configuration parameters of the extractor. Our results are summarized in Chapter 5.

## **1.3** Contributions

This work summarizes the results of three years of individual research on the given topic. The contributions can be identified as follows:

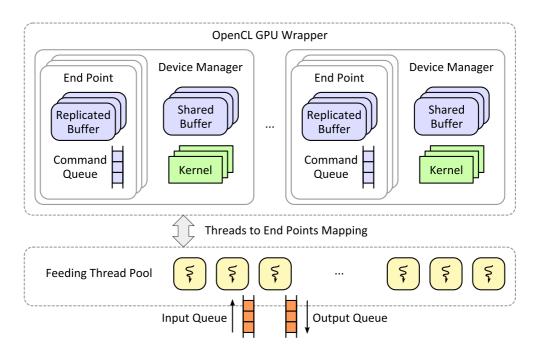

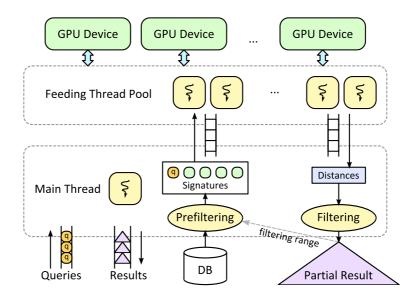

- We have revised the topic of task scheduling in frameworks for parallel data processing and made two improvements [10]. First, we have proposed a new approach for dealing with blocking tasks in parallel frameworks for multi-core CPUs. Second, we have designed our own framework for hybrid CPU-GPU systems. This framework is built on top of the OpenCL library and it simplifies the design of our applications. Furthermore, the proposed idea of the feeding thread pool exhibits significant improvement. It reduced the waiting times during data transfers and allowed us to better utilize the GPU computational power, especially in multi-GPU configurations.

- The domain of similarity search and content-based retrieval is much more computationally demanding, so it can really benefit from the parallel approach. We have adapted a Signature Quadratic Form Distance function, that computes (dis)similarity of two image signatures, for the GPGPU platform [11, 12]. A speedup of two orders of magnitude was observed. Furthermore, we have also accelerated the database access method called the pivot table prefiltering and proposed a novel range estimation algorithm that solves the problem of parallel k nearest neighbour queries.

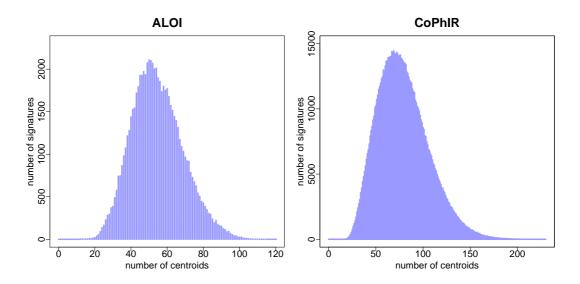

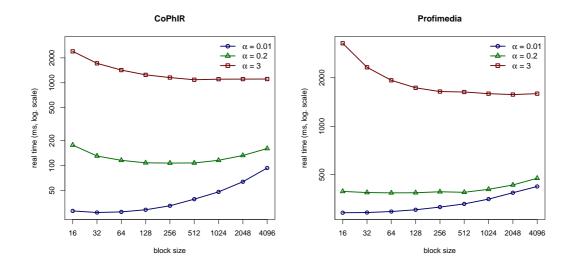

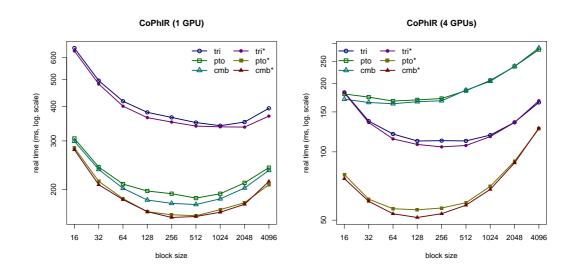

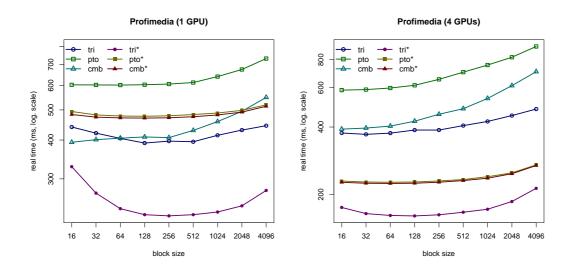

- Finally, we have employed the GPGPU in the database indexing and proposed a GPGPU feature extractor, which computes the signatures for images [13]. This fast extractor opened new possibilities as it allowed us to index large image databases. It also allowed us to explore the configuration parameter space of the extractor and to find a configuration that produces the most accurate signatures. These experiments took only several weeks on the GPU, but they would have taken more than a year using only CPUs.

# 2. Parallel Architectures

Knowing your enemy is the first step in designing a good strategy. To do so, we revise current parallel architectures especially multi-core CPUs and many-core GPUs. As these architectures are quite complex, we narrow our focus only to the aspects that directly influence the design of our parallel algorithms.

# 2.1 Multi-Core CPUs

Multi-core CPUs are well established in the segments of servers, personal computers, and laptops. At present time, they are penetrating to the segment of tablets and mobile phones. Desktop CPUs have up to 16 cores and more cores per chip are expected in future generations. Even though there are many types of processor architectures, we will focus on the Intel IA32 (more commonly known as the x86) architecture, since it is the predominant architecture in personal computers, small servers, and server clusters. Most of the observations made about IA32 hold for other architectures as well and we explicitly point out any important differences.

## 2.1.1 Parallelism in CPUs

Current CPUs employ parallelism on three levels:

- instruction execution,

- vector instructions (data parallelism SIMD),

- and on-chip core replication (task parallelism).

## **Executing Instructions Simultaneously**

The very first computers were designed to execute one instruction at a time. Quite soon, it become clear that this solution is suboptimal as each instruction comprises several smaller steps, such as decoding or activation of some numeric processing unit. A natural solution to this problem is to create an *instruction pipeline*. The pipeline design was first mentioned in the work of Konrad Zuse [14] as it was used in the Z1 and Z3 machines. It was employed on regular scale in the late 1970s, especially in the Cray supercomputers [15].

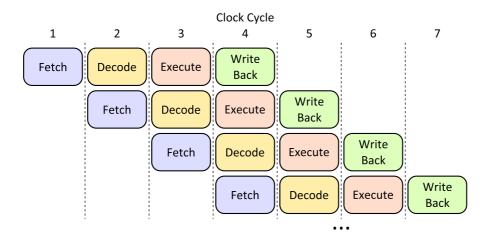

Each instruction is divided into fixed number of steps that are processed by different stages of the pipeline. Separate stages can perform their tasks concurrently, thus the execution of subsequent instructions partially overlap. A simple example of a 4-stage pipeline is depicted in Figure 2.1.

Although the pipeline can increase the instruction throughput significantly, it is encumbered by several problems. Most important are *instruction dependency hazards* and *branching problem*. The first problem is caused by the sequential execution model that is presented to the programmer but not upheld by the pipeline architecture. When instruction inputs depend on the outputs of the previous instruction, the previous instruction needs to be processed entirely (i.e., including

Figure 2.1: An illustrative example of 4-stage instruction pipeline

the write back stage), before the following instruction is executed. Current CPUs deal with this problem by stalling the pipeline or reordering the instructions. The second problem is caused by the uncertainty of conditional jumps. Each conditional jump has two possible results – it is either performed or it is not. This means that the following instruction is not certain until the jump instruction is executed. This problem is usually solved by *branch prediction* and *speculative execution*. The CPU tries to guess, which branch is going to be taken and starts to execute it. If the other branch is taken, the pipeline must be discarded and then repopulated by the correct instruction stream.

The superscalar architecture presents the next level in the instruction parallelism. This architecture was first introduced in CDC 6600 Cray mainframe in 1965 and the first x86 CPU with superscalar architecture was Intel Pentium (P5), released in March 1993. A superscalar processor is capable of executing multiple instructions at once. It is usually based on the pipeline architecture, hence a superscalar CPU has more than one pipeline.

Current CPUs also employ the *out-of-order execution*. The x86 processor family first introduced this feature in Intel Pentium Pro (1995) along with the speculative execution. The out-of-order pipeline can reorder instructions to better utilize computational units of the CPUs and avoid instruction dependencies in the pipeline while maintaining the consistency of the results.

Even though this type of parallelism is very interesting and more advanced optimizations are implemented with every new generation of CPUs, it can be hardly affected by the programmer. The instructions may be generated so that the pipeline and the out-of-order execution works better in some cases; however, these optimizations are performed solely by the compiler.

#### Vector Instructions and Data Parallelism

The single instruction multiple data (SIMD) execution model is based on a simple idea that the processor can perform the same instruction on multiple data simultaneously. This approach is quite conservative and easy to implement as it requires that the processor design duplicates only the execution units (e.g., arithmetic units) and remaining units, such as the instruction decoder, caches, registry, or the data loading/storing units, are shared. Therefore, a vector instruction is treated almost as a regular instruction, except for the execution part which activates multiple symmetric units at once and lets them simultaneously process a vector of numbers instead of a single number.

The x86 family first introduced the MMX vector instruction set in Intel Pentium MMX (1997). It was shortly followed by the 3DNow! technology from AMD (1998) and the Streaming SIMD Extension instruction set (SSE) in 1999. Current x86 processors implement SSE version 4.2, Advanced Encryption Standard (AES), Advanced Vector Extensions (AVX), CVT16, and eXtended Operations (XOP) instruction sets. Most recent instruction sets of fused multiply-add operations (FMA3 and FMA4) have just appeared in the newest AMD processors and are planned for the next generation of the Intel processors. It is safe to say that this level of parallelism has strong support from the CPU vendors, thus we have to embrace it in our software designs.

Fortunately, current compilers are well aware of the vector instruction sets and they try to generate these instructions whenever possible. In complex situations, when the compiler fails to recognize an opportunity to exploit vector instructions, we can optimize critical routines manually by rewriting them in assembly language, or by using some special libraries, such as the xmmintrin.h header, which provides API for vector instructions directly from C/C++ language.

#### Embedding Multiple Cores for Task Parallelism

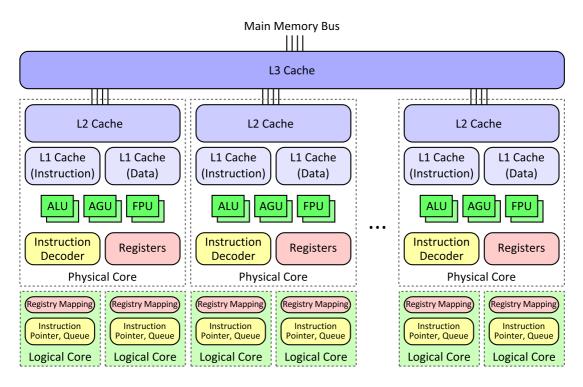

The third level of parallelism is the one that concerns us the most. As the transistors are getting smaller with each new generation of chips, it become possible to integrate multiple CPU cores onto a chip (as depicted in Figure 2.2). These cores are almost as independent as separate processors would be, since they share only communication buses, power management, and top level L3 cache. Each processor core executes separate instruction thread, thus they are perfectly suited for task-parallel problems.

Furthermore, a CPU core has many redundant units. Despite the instruction level parallelism, these units are rarely all occupied. One of the possible solutions is to increase the number of threads processed by the core. It can be achieved by attaching multiple frontends (*logical cores*) to each physical core. The logical cores appear as regular processors to the operating system, but they share many resources of the physical core. The instructions issued to these cores are interleaved in some way, hence they increase the utilization of internal units and mask some of the system latencies.

One of the first systems that implemented this approach was the Delencor HEP [16] in early 1980s. It used multiple blocking threads per core interleaved on cycle-by-cycle basis in a pipeline. Currently, the multithreading technique is implemented in various architectures, such as Itanium (IA-64), IBM POWER5, or UltraSPARC.

The first appearance in the x86 family was in 2002, when Intel introduced new Pentium 4 Netburst architecture [17] with *Hyper-threading* technology [18, 19]. Each core has two logical frontends, thus it processes two independent instruction streams. Intel chose a minimalist approach as they added only the most essential units like registry alias tables or instruction buffers to the chip. Most of the remaining units are either time-shared or partitioned between the two threads.

Figure 2.2: An illustrative schema of a multi-core CPU

AMD implemented their version of multithreading almost ten years later in the Bulldozer architecture [20]. Unlike Intel, the AMD *dual-core modules* actually duplicate many of the units. The idea is to create two cores with much simpler design but dedicated units, especially the L1 cache and the integer execution units. However, some of the parts (like L2 cache, instruction decoder, or floating point units) are still shared between the cores.

As we have mentioned in Chapter 1, the multi-core approach was an answer to the heat problems caused by high operating frequencies. Even though the tradeoff between the number of cores and their frequencies is quite beneficial for large servers and multiprocess environments, there are still applications, which are inherently serial. In order to increase performance of serial problems, most of the current CPUs implement some kind of internal speed regulation (e.g., the Intel Turbo Boost technology). In case some cores are not utilized, the CPU power management turns these cores off and diverts the saved energy to the remaining cores, so they can increase their frequencies as they got more power. This technology must be considered as in some cases it might be better to use a fast serial algorithm instead of an inefficient parallel one.

## 2.1.2 Memory Issues

Most of the tightly coupled parallel systems rely on *shared memory* model, where multiple computational units share their data in one memory space. This model has several important issues that must be addressed, like the synchronization, coherency, performance, or memory protection. We revise issues which are the most important for the design of parallel algorithms.

#### Data Synchronization

In any parallel environment, access to shared assets has to be synchronized. In case of shared memory, access to mutable data structures shared amongst multiple threads must be coordinated to avoid data corruption caused by concurrent read-write and write-write operations. Even though there are many techniques and design patterns [21] that reduce the necessity of synchronization, like data replication or privatization, the synchronization is inevitable in many situations.

The problematics of synchronization has been thoroughly studied [22, 23, 24]. There are basically two ways, how to synchronize access to shared data:

- atomic operations and

- mutual exclusion.

The *atomic operations* are suitable for simple stand-alone updates of the data. An atomic operation is a single instruction that is guaranteed by the system architecture to be performed entirely at once and in a thread-safe manner [25]. The most common operation is the *compare-and-swap* instruction (CAS), also known as compare-and-exchange or test-and-set. The instruction has three operands: old value, new value, and a pointer to variable in main memory. If the variable holds the old value, the new value is atomically assigned to it. Even though we can implement almost anything with this instruction, specialized atomic instructions such as increment, integer arithmetics, or logical functions are implemented by most architectures [25].

If data updates are more complex and the functionality cannot be provided by atomic operations, the *mutual exclusion* needs to be ensured. It is based on the premise, that only one thread may work with the shared data at a time. There are many types of synchronization primitives. The simpler ones use guarding variable (a lock) which is modified by atomic operations (usually the CAS instruction). An active waiting is used in case the lock is acquired by a different thread. A typical representant of such primitive is the *spin-lock*.

More complex primitives like the *mutex*, the *semaphore*, or the *read-write lock* suspend the waiting thread to save computational resources. In order to do so, in addition to guarding variable, they require queues for waiting threads and a mechanism for waking suspended threads.

#### Caches

Memory latency is a serious performance problem since the CPU processing speed significantly outmatches the data throughput of the operating memory. There are various techniques that can be used to reduce memory latency. Common CPUs deal with the problem by employing multi-level caches that selectively store fragments of data which are used by the CPU core at a time (see Figure 2.2). Current x86 CPUs use three-level organization. L1 caches, which are closest to the CPU core, are the smallest (tens of kB) but also the fastest. L3 caches, which are closest to the main memory, are the largest (several MB) and the slowest.

The lower levels of cache (usually L1 and L2) are replicated on every core, while higher levels (L3, sometimes L2) are shared. This presents a potential problem as the same data might be copied and modified in caches of two cores

independently. In order to maintain data integrity, some kind of cache coherency protocol must be employed. The x86 architecture use the *MESI protocol* [25] in combination with *memory bus snooping* technique.

The protocol marks every cache line with label *Modified*, *Exclusive*, *Shared*, or *Invalid*. These labels indicate the replication state of the data. There are simple rules describing which operation is the processor core allowed to do with each line type. The protocol also defines how to change the state of the line if necessary. The processor is snooping on the memory bus and modifies the state of the lines according to the observed memory traffic. This coherency protocol is operating on each level of the cache.

A cache coherency protocol can create an unpleasant side effect called *false* sharing. Since a cache line is usually at least tens of bytes long (64 B in IA32), two threads might be working on independent data which are close enough to fall in the same cache line. In such case, the coherency protocol forces the cores to steal the cache line every time they would like to perform some exclusive operation, thus creating a ping-pong effect on the memory bus. This problem is easily avoided by aligning intensively used data to the cache line boundary.

Even though we have focused on the x86 CPU family, most of other architectures use very similar mechanisms including the cache coherency protocols. These differences are not important from the programming point of view, thus we have chosen not to elaborate on the details.

#### Virtual Memory Space

The memory protection mechanisms used by current operating systems [22, 23] to separate data of different processes introduce virtual memory spaces. Each process is provided with its own virtual memory space, which creates an illusion the process has all the memory for itself. It also prevents the process to see or write the memory of other processes, unless two processes explicitly negotiate some memory sharing.

Virtual memory addresses need to be translated to physical memory addresses. This translation mechanism must be supported directly by the CPU and the operating system must manage the translation mechanism. The IA32 architecture uses page tables to translate the address [25]. Page tables are organized as a widespread shallow tree<sup>1</sup>, which is quickly traversed from root to leaf when a physical address is looked up. Table on each level is indexed directly by a part of the virtual address, thus the *page-walk* is very fast. On the other hand, these tables are present in main memory, thus each translation requires several memory reads.

The main reason, why the virtual address translation is not incredibly slow, is the presence of a dedicated cache for translated addresses called *translation lookaside buffers* (TLB). In order to utilize this cache as much as possible, we should avoid data access patterns that jump over large portions of the virtual memory space. Furthermore, the TLB is cleared every time a process is switched on the CPU core, since the new process has its own memory space. Hence, we should minimize context switches and use threads that share memory space rather than processes with their own memory spaces.

<sup>&</sup>lt;sup>1</sup>With up to 4 levels, depending on address space type and size.

Other architectures use more or less elaborate translation mechanisms. One of them is the *inverted page tables* translation employed by PowerPC, UltraSPARC, or IA-64. The basic idea is to use hashing in order to find translation for an address quickly. Another approach is to use a TLB-only solution with software filling like MIPS processors does. The TLB cache is manipulated by the operating system and cache misses are handled by system exceptions.

#### NUMA Systems

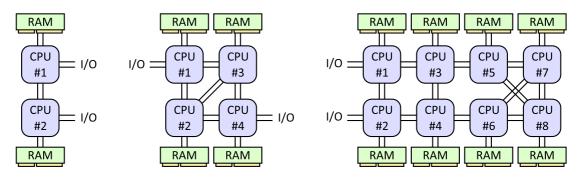

Small symmetric multiprocessor systems are often organized in cache coherent nonuniform memory architecture (ccNUMA) [26]. In this architecture, each (multi-core) processor has its own private memory and it is interconnected with one, two, or even three other processors as depicted in Figure 2.3.

Figure 2.3: Samples of 2, 4, and 8 node NUMA systems

Each node can access not only its own memory, but the memories of other nodes as well. Obviously, data transfers from the local memory of the node are faster than transfers from a memory of another processor. This delay is often called the *NUMA factor* and it can slow the data transfers even several times. Furthermore, it has been observed that when a memory of a processor is accessed by another processor, the first processor is being slowed by the data transfer.

### 2.1.3 API and Parallel Libraries

Parallel execution on multiple cores is achieved by employing multiple processes or by spawning multiple threads within one process. The technical and implementation details are within the realms of the operating system kernel, which is well beyond the scope of this thesis. As we are focusing on high performance data processing applications, we will settle for the simple fact that the underlying operating system allows us to execute multiple threads at once and the threads are executed by available processing units in the best effort manner. Each thread is a piece of code that may run independently (i.e., it has its own state, call stack, etc.), but all threads share the memory, thus they can easily cooperate on a problem.

The threads provide a low-level generic way how to execute code in parallel on multi-core or multi-CPU systems, but they are not very programmer-friendly. To reduce the tedious programmers' work, various parallel libraries, frameworks and application interfaces have been introduced, such as the Intel Threading Building Blocks [27, 28] or the OpenMP [29, 30]. These libraries provide extensions to standard thread programming by offering additional value, such as parallel algorithm templates or data structures designed for concurrent access. In the following, we briefly describe the Intel TBB and some of their generic ideas, as we have used this library in our experiments.

#### Intel Threading Building Blocks

The Intel TBB is an open source multi-platform library for the standard C++ language. Unlike some other libraries it does not provide any language extensions, but it uses C++ templates and other C++ features to provide generic parallel algorithms and data structures in addition to standard things like threads or atomic operations. We introduce some of the most essential structures to illuminate the general idea. More detailed descriptions can be found in Intel documentation [28] and literature [27].

Basic parallel algorithms, which are sometimes called *parallel primitives*, cover the most fundamental problems.

- The *parallel-for* is a template for a typical data parallel task. It traverses a selected index range and invokes a given functor (the body of the parallel loop) for each item in the range (concurrently when possible).

- The *parallel reduce* performs standard tree reduction technique, where leaf operations (computation) as well as joining operations (reduction) are performed in parallel.

- Finally, the *parallel scan* performs the prefix scan operation concurrently. The prefix scan takes a vector  $x_i$  and computes another vector  $y_i$ , where each  $y_i = x_i \oplus y_{i-1}$  ( $y_0 = x_0 \oplus Id_{\oplus}$ ). The  $\oplus$  is an associative operation and  $Id_{\oplus}$  is a neutral item of the  $\oplus$ . Even though the prefix scan looks inherently serial, it can be parallelized at the cost of doing some additional work [27].

Parallel data structures implemented in TBB are basically a thread safe versions of some C++ STL containers. For instance the TBB *concurrent vector* or the *concurrent queue* are very similar to the *vector* and the *dequeue* STL containers, but they can be operated simultaneously from multiple threads or parallel primitives. Others, like the *concurrent hash map*, are specifically designed for concurrent usage and provide a specific API that is both effective and efficient.

#### Task Scheduling

The TBB offers a quite sophisticated task scheduler besides the convenient parallel primitives and containers. This scheduler also works as an engine for the primitives described above. A task scheduler is more convenient than programming with raw threads as it reduces the overhead of creating and disposing of a thread and provides better ways to keep the CPU workload balanced.

The scheduler uses a *thread pool* – a pool of worker threads which are created when the application starts (or when first needed) and destroyed when the application terminates. These threads are waiting on a synchronization primitive until a task is dispatched to them. Waking up a suspended thread is much faster than creating a new one, thus a significant amount of time can be saved. The TBB usually creates as many threads as there are logical cores available. This way, all cores can be occupied if sufficient concurrent tasks are available and the overhead of the operating system scheduler is reduced as the threads do not need to switch between available processors.

The tasks are dispatched nonpreemptively to free threads. If no free thread is available, they are queued and dispatched as soon as one of the worker threads finishes. Since the dispatching overhead is quite low, the programmers are encouraged to produce large quantity of tasks. This technique is called *oversubscription* and it helps to balance the workload. We address this matter more thoroughly in Section 3.2.2.

# 2.2 Many-Core GPUs

A graphical processing unit is a piece of specialized hardware originally designed to encode digital image data into signals that can be directly interpreted by the computer monitor. First GPU cards comprised mostly the video memory connected to digital-analog signal converters, and their programming API provided only very simple 2D operations for copying image data. In 1996, the first 3D accelerator for desktop PCs was presented and the GPU encompassed some basic computational operations required for rendering 3D graphics, such as fast multiplication of small vectors and matrices. Propelled by the gaming industry, the GPU development raced forward and featured new functions like textures rendering or lightning computations.

In 2001, the 3D rendering pipeline was enhanced by introducing small pieces of code called shaders, that can be executed over every vertex of the scene or over every pixel fragment in a highly parallel fashion. The stream processors that execute shaders were quite primitive in the very first version and their program was limited in length, instruction set, and available memory (registers). In the following five years, the stream processors become much more powerful and universal. Finally, in 2006, they have become powerful enough to be used for generic (i.e., not only graphical) computations as well. The GPGPU has emerged as a very strong and cheap parallel platform designed for data parallel problems. As such, it plays and is going to play a significant role in high performance computations.

In this section, we summarize the hardware properties and programming model of current GPUs. Most of the facts and observations are made about NVIDIA Fermi architecture [31], which was the state of the art when our experiments begun. The newest state of the art architecture (NVIDIA Kepler [32]), which emerged in 2012, features some enhancements. However, we do not provide a description of Kepler architecture as all our experiments were conducted on the Fermi GPU cards. At the end of the section, we also provide a brief description of the programming API – the OpenCL library, which was used in our prototype implementations.

The development of GPUs lies solely in the hands of commercial companies, which keep their secrets about implementation details quite safe. We can only summarize information published in programming specifications [33], optimization guidelines [34], and related literature [35], hence our overview might be slightly inaccurate. We describe the hardware model as it appears to the programmer rather than the hardware itself.

### 2.2.1 Hardware Overview

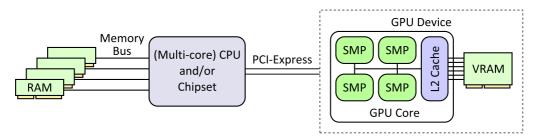

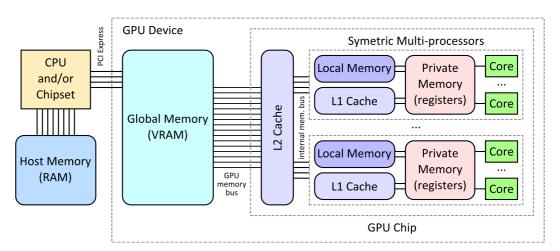

A GPU card is an independent device (see Figure 2.4) with all advantages and disadvantages. The main advantage is that the device can process its own tasks, while other parts of the system, especially the CPU and other GPUs, can perform other work. The main disadvantage is that the GPU card is separate from the host operating memory, hence all input data must be transferred from the host to the GPU internal memory and all results must be transferred back. Furthermore, the CPU cannot interrupt nor interfere with the GPU tasks once they have been dispatched.

Figure 2.4: Schema of a host system with a GPU device

The GPU is interconnected with the host system by an expansion bus, usually the PCI-Express (PCIe). The PCI-Express 2.0 (16×), which was present in our hardware, is capable of transferring up to 8 GB per second in both directions. In comparison with CPU buses, such as Intel QuickPath Interconnect (QPI) or AMD HyperTransport (HT), which both have throughput of approximately 25 GB/s, the PCIe bus is rather slow. Therefore, the data transfer cost must be considered carefully and the GPU should be used only for operations, where the amount of the computational work significantly overweights the data transfers, or when the data transfers can overlap with the computational work.

The device itself is equipped with an internal memory and a GPU processor. They are connected by a wide memory bus which has high throughput – usually over 100 GB/s. Beside the shared memory controller and the L2 cache, the GPU processor is formed by several *Symmetric Multiprocessors* (SMPs). A fully loaded Fermi GPU carries 16 SMPs.

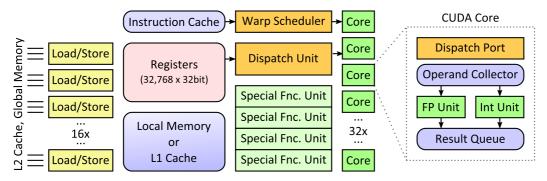

Figure 2.5: Schema of GPU symmetric multiprocessor

The SMP itself (Figure 2.5) consist of several computational cores (32 in case of Fermi). Each core has its own arithmetic units for integer and floating point math and a private set of registers, but they share some resources of the SMP.

Most importantly, the instruction cache, the warp scheduler, and the dispatch unit. These are responsible for the thread planning and the instruction execution, thus all cores must execute the same instruction at the same time. This model is discussed in more detail in the following section (2.2.2). The cores also share load/store units, that are responsible for main memory data transactions, the L1 cache, and the *local memory*. We explain the details of memory structure later, in Section 2.2.3.

### 2.2.2 Execution Model

The GPU devices embrace the data parallel model. In this model, one function (called *kernel*), is invoked multiple times for multiple inputs. The parallelism is achieved by processing these inputs concurrently. This model works perfectly in cases when the kernel function operates solely on the input objects without accessing any other data, thus completely without synchronization. Furthermore, there should be enough data objects to occupy all available processing units to fully utilize the hardware.

When a kernel is invoked, the programmer defines, how many threads it will spawn. All these threads execute the same code with the same arguments, but they are also provided with a *thread ID* value, which can be used to determine the portion of the work (i.e., the input data item) the thread should process. The ID is usually a flat number (from 0 to N - 1 where N is the number of threads spawned), but it can also be a two or three dimensional vector, so the programmer can conveniently navigate in 2D and 3D problems. The threads are lightweight entities as they share almost everything, except for the ID. The programmer is encouraged to create a huge number of threads as the system can easily encompass millions of them. A larger number of threads with smaller tasks to perform creates more balanced workload for the GPU cores.

Threads with adjacent IDs are bundled together in groups. More precisely, the programmer specify the group size G when invoking a kernel<sup>2</sup> and the  $t_{ID}$  thread is placed in the  $\lfloor t_{ID}/G \rfloor$  group. The groups are important from the perspective of scheduling as well as from their perspective of sharing resources, as we will cover later.

#### Single Instruction Multiple Threads

This execution model is an extension of the Single Instruction Multiple Data (SIMD) parallelism which is employed in the CPU vector instructions such as SSE. In this case, we have multiple threads that all have the same code, but they advance through the code together executing the same instruction at a time. However, each thread has its own set of registers, thus working on different data.

This concept is much more powerful than SIMD as the threads have their own memory and even though they must execute the same instruction at a time, they can use branches or even while-loops. Furthermore, the code written for the SIMT model is more clear than a code which contains vector instructions. Finally, the work synchronization amongst the threads is trivial and the barrier instruction is in fact only a simple memory fence.

$<sup>^2\</sup>mathrm{In}$  case of multidimensional IDs, the group size is defined for each dimension.

On the other hand, SIMT execution can be used efficiently only in case all threads have exactly the same amount of work. The main problem is branching. When different threads execute different branches of an if-statement, all cores must execute both branches and some kind of instruction masking technique must be employed, in order to render instructions in the invalid branches inactive. In the worst case scenario, the threads execute a while-loop that terminates early for most of the data, but it can run for a long time in a few isolated cases. If so, most of the cores will linger needlessly in the while-loop masking their instructions while only a few cores will be doing any real work finishing their long-running tasks.

#### Threads on The Symmetric Multiprocessor

Thread scheduler plans thread groups to available SMPs, usually one group to one SMP. Theoretically, there might be multiple groups executing the same kernel mapped to a SMP, if the groups have low requirements and the SMP resources, such as registers or local memory, are underutilized. A thread group is never split amongst multiple SMPs as the threads in the group require access to the local memory.

The group may have more threads than there are available cores on the SMP, so the threads are divided into  $warps^3$ . A warp is a kind of a subgroup with size equal to the number of cores in the SMP. Only one warp is actually running, while other warps are waiting to be scheduled. Threads in one warp are implementing the real SIMT model, as the SMP cores are running in *lock step*, and the threads in one group are running in virtual SIMT. The context switch between two warps is very fast, so the scheduler changes them very often, especially if the running warp becomes stalled (by a memory transaction, for instance).

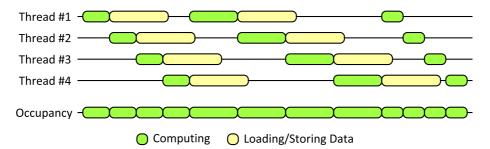

Figure 2.6: Thread overlapping, hiding memory latency

Figure 2.6 depicts the principle of reducing memory latencies by overlapping memory transfers with computations. For instance, when the running warp executes an instruction that loads data from global memory, the load/store units start the memory transaction and the threads must wait for the data. This might be a lengthy operation, so the scheduler switches to another warp which can run meanwhile. The warps are scheduled in a round-robin fashion, thus when the first warp is scheduled again, it is quite likely the data transaction has finished and the warp can continue immediately.

At this point, we need to emphasise an important issue of the thread scheduling. The thread group is assigned to a SMP nonpreemptively. It means that

$<sup>^{3}</sup>$ AMD denotes them *wavefronts*.

all threads must terminate their work before another group is scheduled to that SMP. The context switch of two groups on a SMP would be quite expensive and unnecessary for most data parallel algorithms. On the other hand, there is no way of creating a task synchronization primitive (e.g., a barrier) over all groups, unless we can guarantee that all the groups are assigned to the SMPs and running. Otherwise, any such primitive would most certainly cause a deadlock of the whole system.

## 2.2.3 Memory Structure

The GPU has much more complicated memory model than the CPU. A CPU process perceives the memory as a single uniform space with linear addressing. The GPU process has to deal with several types of memories with different address spaces. Beside the host memory, which is not directly accessible from the kernel, there are following memory spaces:

- a global memory,

- a constant memory,

- a local (shared) memory,

- and a private memory.

Each memory space has separate addressing, thus different type of pointers. The kernel must explicitly declare the type of the address space when creating a pointer and pointers of different address spaces are not compatible.

The memory spaces differ significantly in both size and latency. The memory structure schema, including memory buses and caches, is depicted in Figure 2.7.

Figure 2.7: Structure of memory spaces on GPU

As we have already established in Section 2.2.1, the *global memory* is placed independently on the GPU card. It is several gigabytes large and connected to the GPU chip via an internal memory bus. This bus has a throughput several times higher than QPI, HT, or the integrated memory controller of the CPU, but we have to bear in mind that the GPU memory bus has to feed data to many more processing units. The throughput is achieved mainly by the width of the bus, which has usually at least 256 bits.

The memory controller also connects the global memory with the PCI-Express bus. When the host system wants to exchange data with a GPU device, the data are stored to or loaded from the global memory. Fortunately, current global memory controllers are capable of conducting data transfers to the host system and to the GPU core chip simultaneously, so the memory transactions and the computations can overlap.

The GPU chip is equipped with a transparent L2 cache (768 kB on Fermi) which is shared amongst the SMPs. It caches data from the global memory to reduce the number of data transactions on the external bus.

Each SMP has a small amount (64 kB) of integrated memory shared amongst the cores. This memory is divided between the *local memory*<sup>4</sup> and the transparent L1 cache. The exact division can be configured, but we have usually used 48 kB of local memory and 16 kB of cache.

The local memory is very important for code optimization. It is quite small, but on the other hand it is almost as fast as the registers and it is accessible by all the cores. If the code running on the SMP is optimized to use local memory as manually managed cache or for shared intermediate results, it has significant positive impact on the processing speed.

The private memory belongs exclusively to a single thread and corresponds to the registers of a GPU core. In fact, the registers belong to the SMP (32k of 32-bit words on Fermi) and they are allocated for the threads assigned to the SMP to create an illusion that each thread has a processing core for itself and avoid register saving/restoring when the warp is switched. If we use 512 threads in the group (which is also the current maximum), each thread will only have 64 words of private memory. The compiler may attempt to avoid the problem of limited private memory by spilling the private data to the L1 cache; however, this comes with a serious performance hit due to the increase in memory traffic and instruction count.

Finally, the *constant* memory is a small block of memory dedicated for immutable data shared amongst the threads. It has very limited size (64 kB), but since the data are constant, it can be cached very well, thus accessed quite fast.

### 2.2.4 Memory Performance Issues

There are two important issues concerning the architecture of the GPU memory that strongly affect the performance:

- the global memory data transfers

- the local memory organization

Data transfers between the global memory and the GPU chip are performed in transactions. Each transaction transfers an aligned data block of fixed size.

<sup>&</sup>lt;sup>4</sup>NVIDIA designates this type of memory the *shared memory*. It is also used for texture data in 3D graphic, thus it was formerly denoted the texture memory or the texture cache. The term local memory comes from OpenCL specification, so we will hold to that to avoid ambiguity with the algorithm descriptions.

If the caching is turned on, each transaction transfers a cache line of 128 bytes. The 128 B corresponds to 32 4-byte words, so if all the cores in the warp read or write 4-byte words from within a 128 B aligned memory block, the data are transferred in one transaction. If the memory access pattern is less coalesced, it breaks down to multiple transactions, 32 in the worst case scenario.

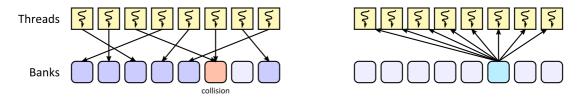

The second issue is the organization of the local memory. The local memory is usually accessed by all 32 cores at once so it must be designed for highly parallel access. Since one memory controller would present a significant bottleneck, the memory is divided into 32 *banks*. Two consecutive 4-byte words are in two consecutive banks (modulo the number of banks). Banks operate independently, so if two threads access data in different banks, the operations are performed concurrently. On the other hand, if two threads access data in the same bank, their operations are serialized and the whole warp is delayed. In a special case when multiple threads read exactly the same word from the local memory, the memory controller broadcasts the value to the threads in one step. The banking principle is depicted in Figure 2.8.

Figure 2.8: Threads accessing local memory randomly (on the left) and the broadcast optimization (on the right)

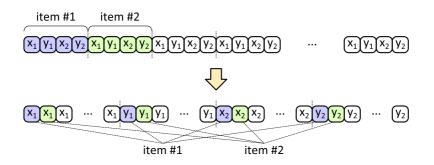

The issues described above lead to an optimization technique frequently employed in GPU programming. In most cases, the data should be organized as a *structure of arrays* instead of an *array of structures*. We can demonstrate the benefits on a simple study case.

Let us have a large number of 2D point pairs for which we want to compute the Euclidean distance:

$$d(i,j) = \sqrt{(x_i - x_j)^2 + (y_i - y_j)^2}$$

On a CPU, we would organize the data as an array of structures, where each structure contains the pair of 2D coordinates (values  $x_1, y_1$  and  $x_2, y_2$ ). This practice is naturally embraced by the programmers as it is more comprehensible in the code and the CPU will deal with it quite well. If we use this organization on a GPU (assuming all values are 32 bit floats), we will create a few small problems. In the following example, the variables are always denoted  $x_1, y_1, x_2$ , and  $y_2$  even though each thread is assigned its own set of these variables.

When a warp loads  $x_1$  values form the global memory, the data are stridden since there is  $y_1$ ,  $x_2$ , and  $y_2$  value between each two adjacent  $x_1$  values. This load will result into four memory transactions instead of one. Thanks to the L2 and L1 cache, the problem would not be so severe as the subsequent loads of  $y_1$ ,  $x_2$ , and  $y_2$  values will be performed from the cache.

If the input point coordinates are stored in the local memory (e.g., as an intermediate result produced by the previous computational step), the situation

gets much worse. When a warp accesses each variable, the values are spread amongst 8 banks instead of 32. There are 4 threads competing for access to each of these 8 banks, thus the whole process is slowed by the factor of four.

Figure 2.9: Data organized as an array of structures and structure of arrays

We can organize our data as a structure of arrays (the difference is depicted in Figure 2.9). If we do so, the loading from the global memory will result in one memory transaction per each variable, thus producing more stable workload. In case of the local memory scenario, two consecutive  $x_1$  variables are in consecutive banks, thus accessing them would not produce any bank conflicts.

### 2.2.5 GPU Programming

There are currently three frameworks that can be used for parallel GPGPU programming – CUDA [36], AMD Accelerated Parallel Processing SDK [37], and OpenCL [38]. The CUDA is a proprietary solution of the NVIDIA company and it is working on NVIDIA hardware only. On the other hand it is well established and quite easy to use, as it is designed solely for GPUs. The APP SDK (originally named *Stream SDK* or *Close-to-Metal*) is a proprietary solution for AMD devices. The AMD solution arrived later than CUDA and it did not reach the same popularity.

OpenCL, on the other hand, is a generic framework for parallel computing designed by the Khronos consortium representing many large companies. It has several implementations for GPUs (from NVIDIA, AMD, or Apple), so it can be used with various devices from various vendors. Furthermore, it encompasses also other parallel devices, such as multi-core CPUs, IBM Cell cards, etc. We have used the OpenCL in most of our experiments since we prefer an open solution to the private one. However, the algorithms and the optimization techniques presented in this work can be applied for any CUDA or APP implementations as well.

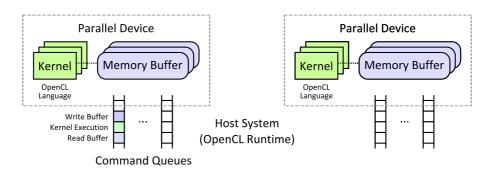

We briefly describe basic principles of the OpenCL framework as some of these principles are quite important for the algorithm design. The framework itself has two parts. On the host side, the *OpenCL runtime* provides an API with bindings to various languages that allow programmer to detect parallel devices and use them. For the devices themselves, the framework defines an *OpenCL language*, which is a subset of C99 language for programming kernels, and a list of built-in functions that must be implemented on the device (thread identification, atomic operations, mathematical functions, etc.).

#### **OpenCL** Runtime

The host-side libraries provide mechanisms to detect parallel devices and list important information about them, such as the number of computational cores, operating frequencies, or the amount of internal memory. When a parallel device is detected, the OpenCL can compile kernels directly for it. Runtime compilation produces much more efficient code, which is optimized for the target device. On the other hand, the kernel compilation itself takes some time. It does not usually bother us gravely as this time can be hidden in the start-up time of the parallel application or in the initialization procedures like the SQL PREPARE statement.

The OpenCL also manages the memory of the parallel device. The memory is allocated via memory objects. A memory object (buffer) is a logical entity that represents a continuous block in the memory of the device. The user cannot define, how or where the object is allocated as these details are implementation specific. The OpenCL defines a set of functions for transferring data to and from the buffers and the buffers can be assigned to kernel arguments in the form of global memory pointers.

Figure 2.10: A model of OpenCL runtime entities

All operations performed on the device are issued through a *command queue*. One or more command queues can be created for each detected device. The most common commands are the read/write operations that manipulate data in memory buffers and the kernel executions. The whole schema is depicted in Figure 2.10.

#### Kernel Execution

When a kernel is executed, it is provided with a *global work size* and a *local work size*. The global work size defines the total number of work items spawned, while the local size specifies the number of items in a group. The work items directly correspond to the threads and the work group is in fact the thread group on the GPGPUs. All the work groups must have the same amount of threads, hence the global work size must be divisible by the local work size.

The work items can be organized into one, two, or three dimensional space and the global work size and the local work size values are specified for each dimension independently. The OpenCL language defines specific built-in functions that allow the work item (the thread) to get the values of work sizes, the work dimension, and the index of the item among the global work load and within the work group.

### **OpenCL** Language

The OpenCL language is a subset of the C99 language [39] with some extensions. The most important differences are:

- Each pointer has an additional type (global, local, or private) that defines its address space (as we have already described in Section 2.2.3).

- The kernel cannot allocate memory. Private memory is assigned automatically to local variables, local and global memory must be preallocated before the kernel is executed.

- There is no stack. All function calls are inlined, recursion is not permitted.

- Fixed-size vector data types are introduced. Each basic type (like int or float) has a corresponding vector type of length 2, 3, 4, 8, and 16 (e.g., uint4 is a vector of four unsigned integers). All basic arithmetic operations defined for the scalar types are defined for the vector types as well. These operations may be translated into fewer instructions if the architecture supports them.

Finally, we have to keep in mind that items in a group can be executed in SIMT or virtual-SIMT fashion. Therefore, an extensive usage of if-statements or while-loops ought to be discouraged.

# 3. Task Scheduling

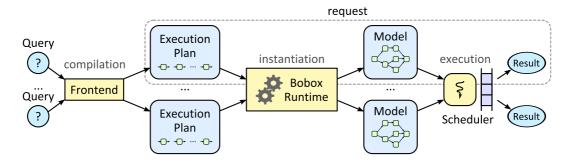

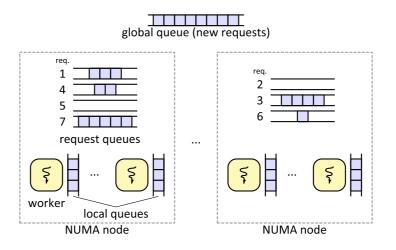

In this chapter, we address several issues of the task scheduling. After a general overview of the topic, we focus on two specific problems of scheduling – the blocking tasks and the hybrid CPU-GPU tasks. We propose practical solutions for these problems and evaluate their impact experimentally.

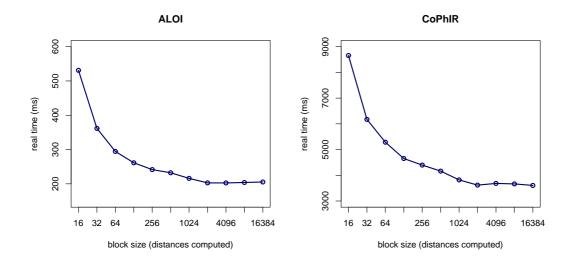

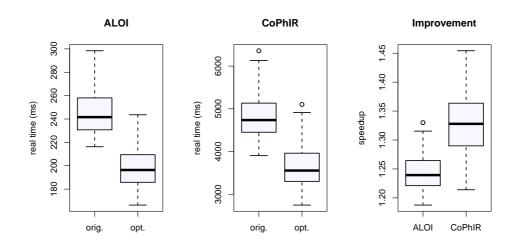

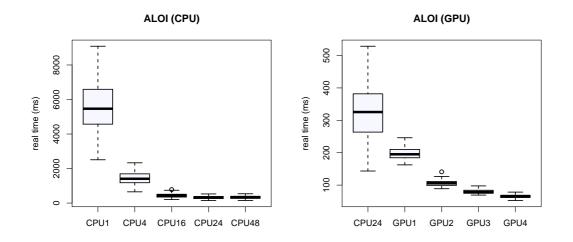

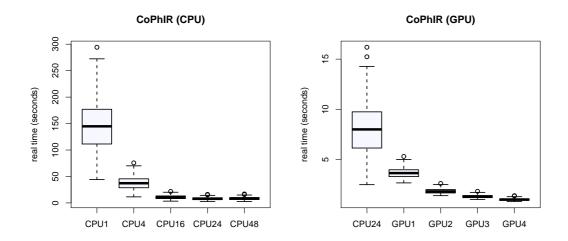

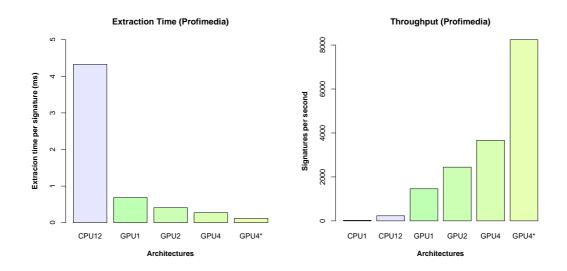

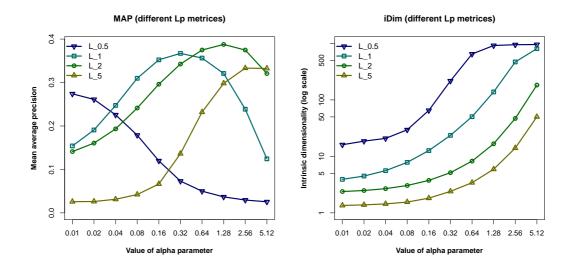

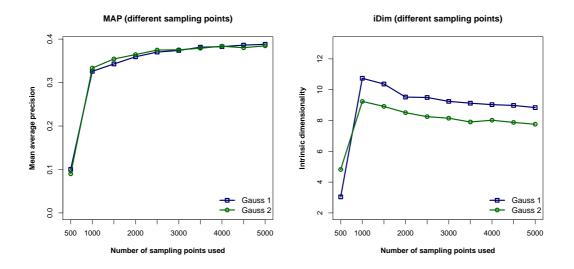

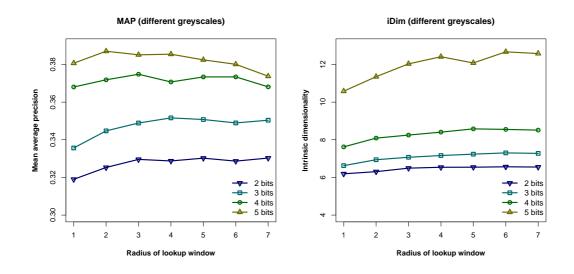

# 3.1 The Problem of Scheduling