UNIVERZITA KARLOVA V PRAZE MATEMATICKO-FYZIKÁLNÍ FAKULTA

# DIPLOMOVÁ PRÁCE

Bc. Václav Klecanda

# Implementace algoritmů pro zpracování obrazu na IBM Cell

Kabinet software a výuky informatiky Vedoucí diplomové práce: Mgr. Václav Krajíček Studijní program: Informatika, softwarové systémy Rád bych poděkoval magistru Václavu Krajíčkovi za jeho vedení, rady, názory a připomínky a vůbec za jeho podporu. Dále chci poděkovat svým rodičům a mé přítelkyni za trpělivost.

I would like to thank to Mgr. Václav Krajíček for leading, his advices, opinions and other support. I also want to thank to my parents and to my girlfriend for their patience during works on this thesis.

Prohlašuji, že jsem svou diplomovou práci napsal samostatně a výhradně s použitím citovaných pramenů. Souhlasím se zapůjčováním práce.

V Praze dne 4. Srpna 2009

Václav Klecanda vlastnoruční podpis

# Contents

| 1 | Intr | oduction                                                | 9  |  |  |  |  |  |  |  |  |  |  |

|---|------|---------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

| 2 | Cell | /B.E. platform 1                                        | 1  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | •                                                       | 13 |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  |                                                         | 13 |  |  |  |  |  |  |  |  |  |  |

| 3 | Cell | /B.E. programming 1                                     | 15 |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Cell/B.E. platform development                          | 15 |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  |                                                         | 6  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3  | Parallel systems & Cell/B.E                             | 17 |  |  |  |  |  |  |  |  |  |  |

|   | 3.4  |                                                         | 8  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.1 Cell/B.E. parallelism levels                      | 19 |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.2 Computation configurations                        | 20 |  |  |  |  |  |  |  |  |  |  |

|   | 3.5  | Building for the Cell/B.E                               | 22 |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.5.1 Process of application porting for the Cell/B.E 2 | 22 |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.5.2 SPE porting considerations                        | 25 |  |  |  |  |  |  |  |  |  |  |

|   |      |                                                         | 26 |  |  |  |  |  |  |  |  |  |  |

|   | 3.6  | Profiling                                               | 27 |  |  |  |  |  |  |  |  |  |  |

| 4 | Ima  | ge segmentation 2                                       | 28 |  |  |  |  |  |  |  |  |  |  |

|   | 4.1  | Problem formulation                                     | 28 |  |  |  |  |  |  |  |  |  |  |

|   | 4.2  | Image segmentation methods overview                     | 29 |  |  |  |  |  |  |  |  |  |  |

|   | 4.3  | Level set                                               | 31 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.1 Level set theory                                  | 32 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.2 Level set computation                             | 32 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.3 Speed-up approaches                               | 33 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.4 Level set image segmentation                      | 86 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.5 Level set methods on streaming architectures      | 38 |  |  |  |  |  |  |  |  |  |  |

| 5 | Desi | gn and implementation 4                                 | 10 |  |  |  |  |  |  |  |  |  |  |

|   | 5.1  | 5.1 Original idea of the porting process                |    |  |  |  |  |  |  |  |  |  |  |

|   | 5.2  | Chosen algorithm and frameworks                         | 11 |  |  |  |  |  |  |  |  |  |  |

|   | 5.3  | Incorporation into MedV4D framework                     | 11 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.1 Client part                                       | 13 |  |  |  |  |  |  |  |  |  |  |

|   |      | •                                                       | 15 |  |  |  |  |  |  |  |  |  |  |

|   | 5.4                                                                         | Level set segmentation pipeline                                                                                                                                                                                                              | 46                                                       |

|---|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 5.5                                                                         | Pre-porting steps                                                                                                                                                                                                                            | 47                                                       |

|   | 5.6                                                                         | Profiling                                                                                                                                                                                                                                    | 49                                                       |

|   | 5.7                                                                         | New design                                                                                                                                                                                                                                   | 50                                                       |

|   |                                                                             | 5.7.1 Data flow                                                                                                                                                                                                                              | 51                                                       |

|   |                                                                             | 5.7.2 Tools                                                                                                                                                                                                                                  | 52                                                       |

|   |                                                                             | 5.7.3 Work balancing                                                                                                                                                                                                                         | 54                                                       |

|   | 5.8                                                                         | Actual porting process                                                                                                                                                                                                                       | 54                                                       |

|   |                                                                             | 5.8.1 PC as Cell/B.E. simulator                                                                                                                                                                                                              | 54                                                       |

|   |                                                                             | 5.8.2 Moving to PPE                                                                                                                                                                                                                          | 55                                                       |

|   |                                                                             | 5.8.3 Tools porting                                                                                                                                                                                                                          | 55                                                       |

|   |                                                                             | 5.8.4 Memory checking tools                                                                                                                                                                                                                  | 55                                                       |

| 6 | Rest                                                                        | llts                                                                                                                                                                                                                                         | 57                                                       |

| - | 6.1                                                                         | Speed measurements                                                                                                                                                                                                                           | 57                                                       |

|   | 6.2                                                                         | Reasons of slowdown and possible improvements                                                                                                                                                                                                | 58                                                       |

|   | 6.3                                                                         | Code and design complexity                                                                                                                                                                                                                   | 61                                                       |

| 7 | Con                                                                         | clusion                                                                                                                                                                                                                                      | 63                                                       |

| ٨ | Ima                                                                         |                                                                                                                                                                                                                                              | 67                                                       |

| A | Imag                                                                        |                                                                                                                                                                                                                                              | 07                                                       |

| B | Tool                                                                        |                                                                                                                                                                                                                                              |                                                          |

| - | 1001                                                                        | s setup                                                                                                                                                                                                                                      | 72                                                       |

| - | B.1                                                                         | s setup<br>SDK installation                                                                                                                                                                                                                  | <b>72</b><br>72                                          |

| - |                                                                             | SDK installation                                                                                                                                                                                                                             |                                                          |

| _ |                                                                             | SDK installation                                                                                                                                                                                                                             | 72<br>74<br>74                                           |

| _ | B.1                                                                         | SDK installation                                                                                                                                                                                                                             | 72<br>74                                                 |

| _ | B.1                                                                         | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_image                                                                                                                     | 72<br>74<br>74                                           |

| _ | B.1                                                                         | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_imageB.2.3Copying content into sysroot_image                                                                              | 72<br>74<br>74<br>75                                     |

| _ | B.1                                                                         | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_image                                                                                                                     | 72<br>74<br>74<br>75<br>77                               |

| _ | B.1                                                                         | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_imageB.2.3Copying content into sysroot_image                                                                              | 72<br>74<br>74<br>75<br>77<br>77                         |

| _ | B.1<br>B.2                                                                  | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_imageB.2.3Copying content into sysroot_imageB.2.4Simulator hints                                                          | 72<br>74<br>75<br>77<br>77<br>77<br>78<br>78             |

| _ | B.1<br>B.2<br>B.3                                                           | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_imageB.2.3Copying content into sysroot_imageB.2.4Simulator hintsUsing examples                                            | 72<br>74<br>75<br>77<br>77<br>77<br>78<br>78<br>78<br>79 |

| _ | B.1<br>B.2<br>B.3<br>B.4                                                    | SDK installation                                                                                                                                                                                                                             | 72<br>74<br>75<br>77<br>77<br>77<br>78                   |

| _ | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> </ul> | SDK installationB.1.1Bug fixingIBM Full-System SimulatorB.2.1Bug fixingB.2.2Installation of libraries into sysroot_imageB.2.3Copying content into sysroot_imageB.2.4Simulator hintsUsing examplesTuning memory usage on PS3Performance tools | 72<br>74<br>75<br>77<br>77<br>77<br>78<br>78<br>78<br>79 |

# **List of Figures**

| 2.1         |                                                            | 12 |

|-------------|------------------------------------------------------------|----|

| 2.2         | Cell/B.E. based machines                                   | 14 |

| 3.1         | 0 0                                                        | 20 |

| 3.2         |                                                            | 21 |

| 3.3         | PPE centric configuration                                  | 21 |

| 3.4         | SPE binary embedding                                       | 23 |

| 3.5         | Application porting cycle                                  | 25 |

| 4.1         | Flooding an object                                         | 31 |

| 4.2         | Narrow band computation illustration                       | 33 |

| 4.3         |                                                            | 35 |

| 4.4         | Graph of thresholding based speed function                 | 37 |

| 4.5         | Leaking                                                    | 37 |

| 4.6         | GPU virtual memory                                         | 39 |

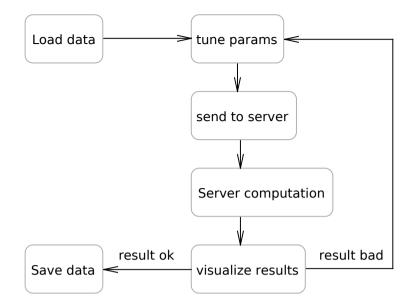

| 5.1         | LevelSetClient application computation process             | 42 |

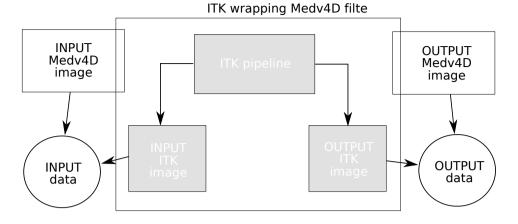

| 5.2         |                                                            | 43 |

| 5.3         | Remote MedV4D filter                                       | 44 |

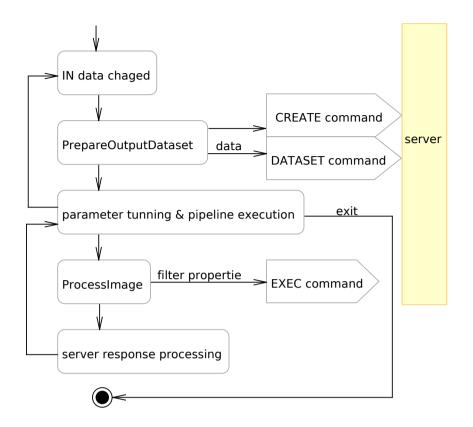

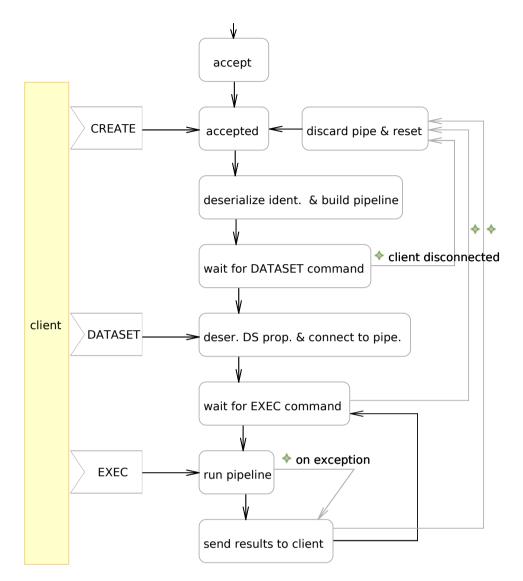

| 5.4         |                                                            | 45 |

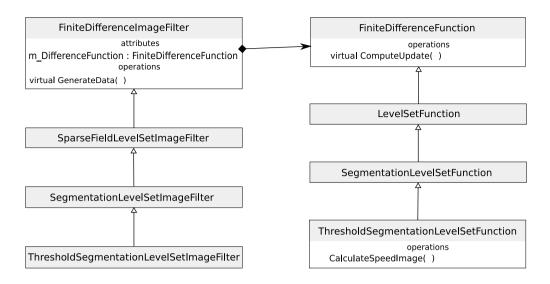

| 5.5         | Original ITK thresholding level set filter class hierarchy | 48 |

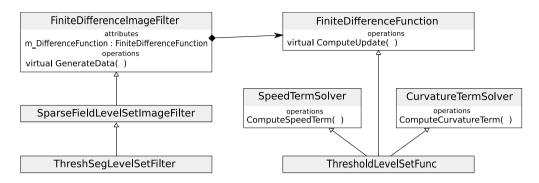

| 5.6         | Resulting level set filter ready to be ported to Cell/B.E. | 49 |

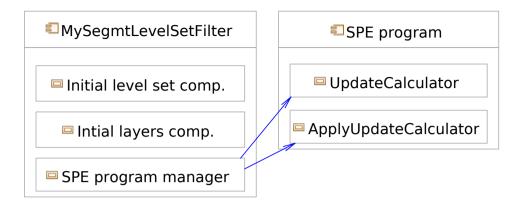

| 5.7         | Diagram of new design components                           | 50 |

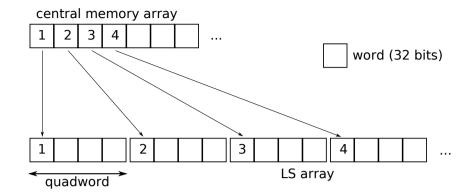

| 6.1         | Automatic align of small data                              | 59 |

| 6.2         |                                                            | 59 |

| 6.3         |                                                            | 60 |

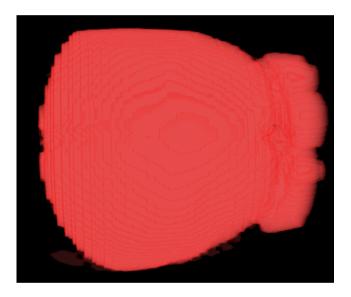

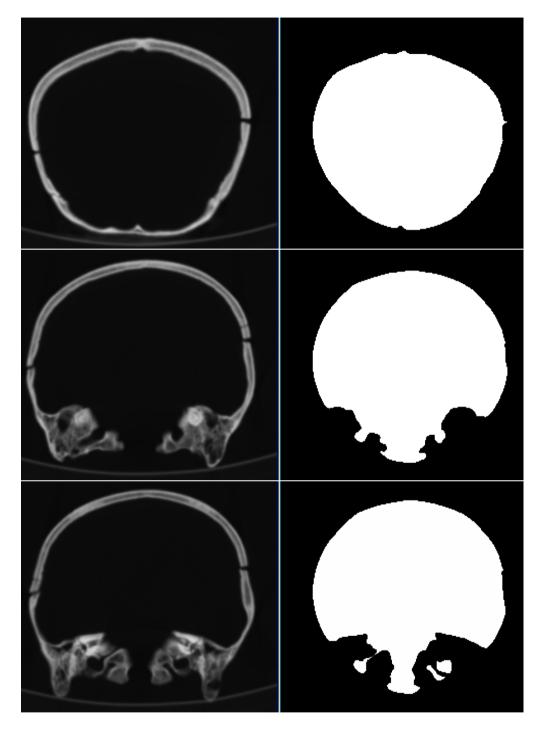

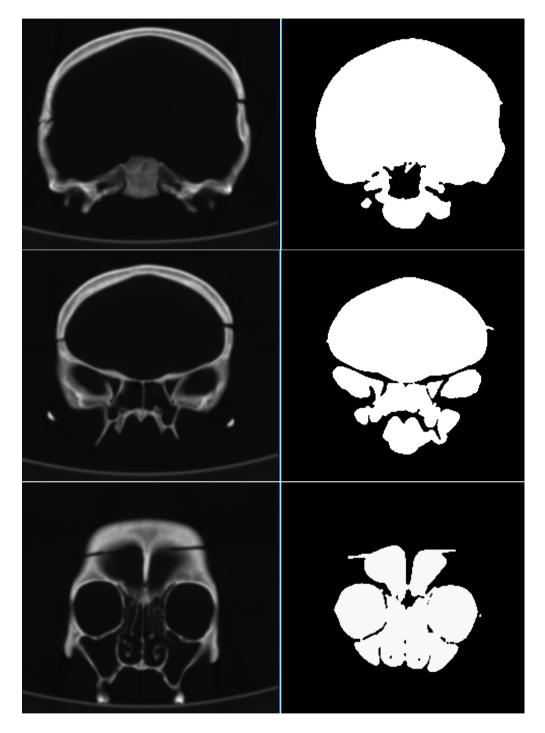

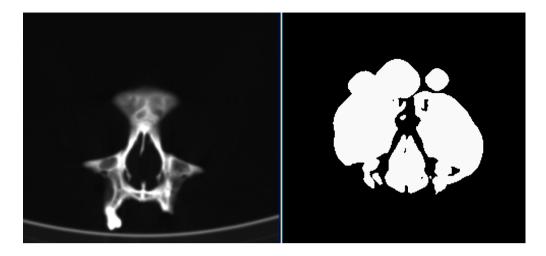

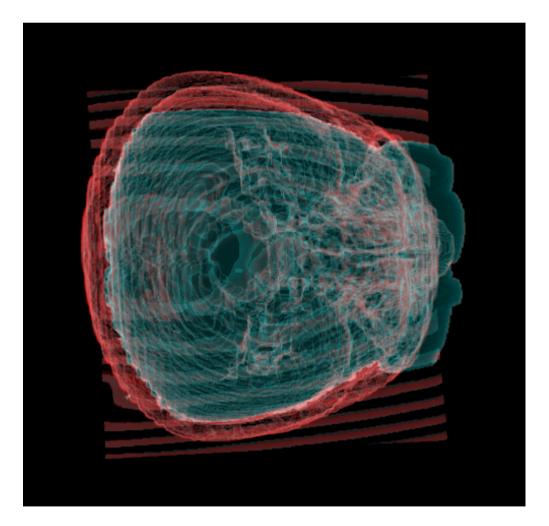

| A.1         | 3D view of segmented skull data set                        | 67 |

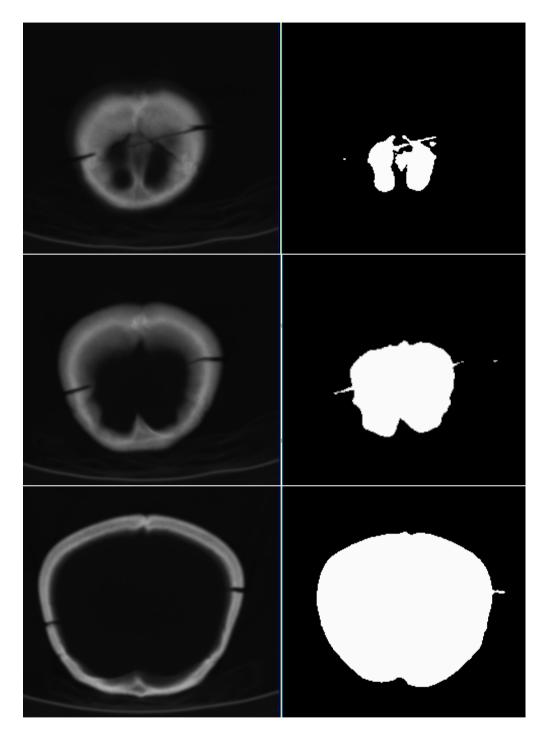

| A.2         |                                                            | 68 |

| A.3         |                                                            | 69 |

| A.4         | -                                                          | 70 |

| A.5         |                                                            | 71 |

| A.6         |                                                            | 71 |

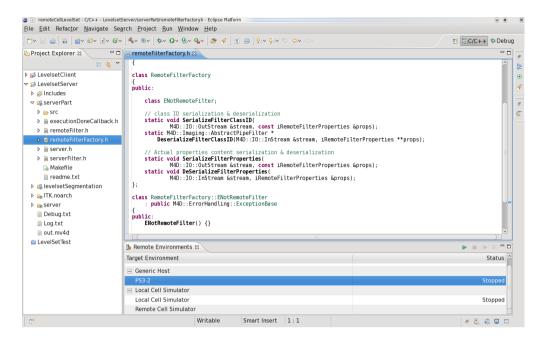

| <b>B</b> .1 | Screenshot of standard cellide veiw                        | 75 |

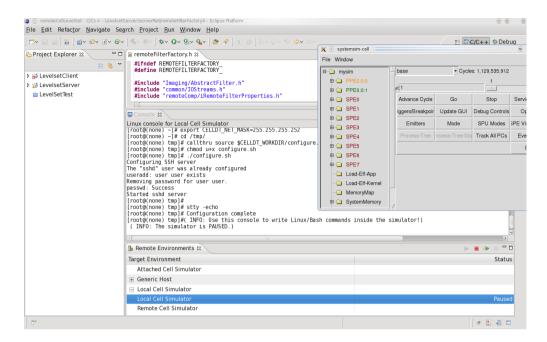

| B.2         | Cellide with started simulator                             | 76 |

# **List of Tables**

| 5.1 | Profiling results   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 49 |

|-----|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 6.1 | Measurement results |   |   |   |   |   | • | • | • | • | • |   |   |   | • | • | • | • | • | • |   |   |   |   |   | • | 58 |

Název práce: Implementace algoritmů pro zpracování obrazu na IBM Cell Autor: Bc. Václav Klecanda Katedra (ústav): Kabinet software a výuky informatiky Vedoucí diplomové práce: Mgr. Václav Krajíček e-mail vedoucího: Vaclav.Krajicek@mff.cuni.cz Abstrakt:

Práce shrnuje dostupné informace o architektuře IBM Cell/B.E. tak, aby čtenář rychle získal potřebný náhled na problematiku programování pro tuto architekturu. Praktické informace jsou čerpány z vývoje aplikace která implementuje netrivialní algoritmus z oblasti zpracování obrazu, sparse field level set segmentation. Další část obsahuje popis vývoje této aplikace a řešení problémů, které mohou během něj nastat.

Práce zároveň srovnává klasickou a Cell architekturu a popisuje nutné podmínky pro vytvoření efektivní aplikace pro Cell/B.E. Dále obsahuje stručný postup instalace nejdůležitějších vývojových nástrojů. Tento postup si klade za cíl co nejrychleji připravit vše potřebné a zkrátit tak dobu přípravné fáze tak, aby čtenář mohl začít vyvíjet pro Cell/B.E.

Klíčová slova: programování pro Cell, multicore acceleration, IBM, PS3

Title: Implementation of image processing algorithms on IBM Cell Author: Bc. Václav Klecanda Department: Department of Software and Computer Science Education Supervisor: Mgr. Václav Krajíček Supervisor's e-mail address: Vaclav.Krajicek@mff.cuni.cz Abstract:

This work summarize available information about IBM Cell/B.E. architecture to let the reader create a necessary overview for programming for this architecture. Practical information are based on development of an application that implements nontrivial image processing algorithm, sparse field level set segmentation. Next section contains description of the application development and associated problems solving.

The work compares common and Cell B.E. architectures and describes conditions necessary for creation of an effective Cell/B.E. application. The work also contains brief procedure of the most important development tools installation. This procedure has to prepare everything necessary as fast as possible and thus to shorten the duration of the preparation phase to let the reader to start development.

Keywords: CellBE programming, multi-core acceleration, IBM, PS3

# **Chapter 1**

# Introduction

The production of x86 platform processors has started a big frequency competition. The manufacturers have been releasing processors with higher and higher operating frequency. Behind this competition there has been a significant amount of research of new production technologies that allow to integrate more transistors onto a smaller area. Gradually the manufacturers started to realize that it is impossible to continue the competition forever.

More computing units started to be integrated into a single processor. The first among common desktop processors was Intel's Pentium<sup>®</sup> with hyper-threading. This processor was able to execute two threads at a time. Since then a quick boom of multi-core integration started even among other big processor manufacturers.

Integration of more execution cores allows less power consumption. This factor is nowadays especially important due to processor integration into laptops and even due to environmental issues. Therefore current effort of the processor manufacturers is to gain the best performance to power consumption ratio.

General purpose cores are integrated into the current common processors. It means they have a pipeline for instruction execution composed of several stages. Instruction can be in various states in the pipeline, e.g. fetched, awaiting operands, ready, executed. Instructions do not flow among the stages in the order that designates the program but the order is decided by the processor itself. The decision is based on variety of factors and predictions. One of the pipeline stages is a branch-prediction unit. It has to predict the most probable flow of the executed program. When this prediction is false the whole pipeline has to be discarded and execution of the right branch of the program has to be started. Processors suffer heavily from these mispredictions because they lead into big execution holes in which the processor pipeline stalls or is being reset.

#### CHAPTER 1. INTRODUCTION

Cache misses are another general purpose processor suffering. A cache miss occurs when the requested data are not within processor cache and have to be loaded from the main memory.

Although many improvements were implemented into the general purpose processors they still suffer from the described problems. This is one of the reasons why a collaboration of three big companies IBM, Sony, and Toshiba started development of the Cell/B.E. processor. It is a multi-core processor which has high performance to power consumption ratio and is able to overcome the problems that the general purpose processors suffer from. That is because it allows the programmer to manage processor cache and branch prediction unit to a certain degree. The next chapter will describe the processor in more details.

# **Chapter 2**

# **Cell/B.E. platform**

This chapter will introduce the Cell Broadband Engine processor (Cell/B.E.), the whole platform and its specific details. The particular Cell/B.E. processor will be described and illustrated. All the information were taken from [6].

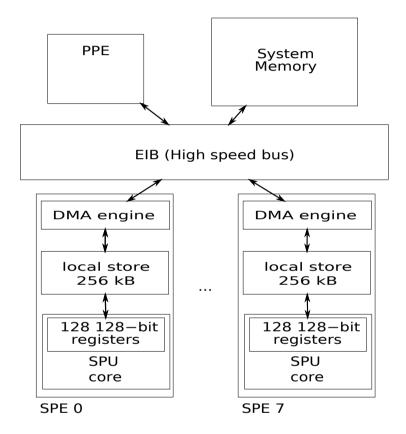

Cell/B.E. processor is representative of a new generation of IBM's Cell/B.E. platform family. Cell/B.E. is an asymmetric, high-performance multi-core processor that combines eight synergistic processing elements (SPE) and a Power Processing Element (PPE), which is a general-purpose IBM Power  $PC^{(\mathbb{R})}$  core. The next important part is a central memory element. The PPE can operate with the central memory directly while the SPE can access the memory indirectly through DMA. All the elements are connected through a high speed bus (EIB - Element Interconnect Bus). The whole layout is in the figure 2.1.

The Cell/B.E. achieves a significantly better performance per Watt and performance per chip area ratios than conventional high-performance processors. It is more flexible and programmable than single-function and other optimized processors such as graphics processors, or conventional digital signal processors. While a conventional microprocessor may deliver about 20+GFlops of single-precision (32b) floating-point performance, Cell delivers 200+ GFlops (under ideal conditions) at a comparable power consumption.

A number of signal processing and media applications have been implemented on the Cell/B.E. with excellent results. Advanced visualization techniques such as ray-casting, ray-tracing and volume rendering, streaming applications such as media encoders, decoders or encryption and decryption algorithms have also been demonstrated to perform about an order of magnitude better than a conventional processors.

Figure 2.1: One PPE unit along with eight SPE stream processor units and system memory connected together with a high speed EIB bus

### 2.1 PPE - Power Processing Element

The PPE is derived from IBM Power  $PC^{\mathbb{R}}$  core. It has 512kB L2 on die cache. It supports the Power Architecture ISA, inherits the memory translation, protection, and SMP coherence model of mainstream 64-bit Power processors. Virtualization, logical partitioning, large pages, and other recent innovations in the Power architecture are supported as well. Programming for the PPE is the same as for conventional processors due to direct access to central memory.

### 2.2 SPE - Synergistic Processing Element

SPE is an autonomous processor (sometimes called accelerator) targeted for computational intensive applications. Each SPE has a SIMD core (SPU), a high-speed private local store memory and a direct memory access (DMA) engine.

The SPU unit has 128 128-bit wide unified general purpose registers to store all types of data in contrast to traditional RISC processors where registers are divided according data types. It supports a SIMD-RISC instruction set. The SPU has two pipelines, the odd one and the even one, so it can execute two instructions at a time (dual-issue) if some conditions are met. Vectorized operations in various data types configurations can be performed with these registers e.g. two doubleprecision floats or eight 32bit integers can be processed at single clock tick.

Unlike conventional microprocessors the SPE does not have a hardware cache. Its function represents the small on-chip local store memory under programmer's control. This allows code optimizations that can reduce cache misses. The local store is separated from the main memory i.e. the SPE has its own address space. Therefore any synchronization with other cores is not necessary. The SPE uses the local store as a cache of data stored in the central memory i.e. programmer has to create copies of the data within the local store. The data are transferred through DMA engine which manages transferring data from central memory to local store and vice versa as well as between two SPEs' local stores. We say that data is "DMAed" from source to destination. DMA commands can be issued in many ways such as in synchronous, asynchronous or in scatter-gather manner through DMA lists. The DMA list is an array of pointer-size pairs that defines pieces of memory that shall be transferred within single DMA request. The pieces must not necessarily be continuous. Therefore the Cell/B.E. processor can be viewed as a distributed memory multiprocessor. The local store memory management is a big part of programming for the Cell/B.E.

Programming for the SPE is a bit different compared to programming for a conventional processor. Programmer have always to count with the fact that he/she

Figure 2.2: Images of Cell/B.E. based machines. Sony's Play Station 3, on the left (image taken from www.boygeniusreport.com), IBM Cell Blade board, on the right (image taken from www.ps3tester.com)

has only 256kB for the program and data. More details about this topic will be described in the next chapter.

The Cell/B.E. is embedded in game console Sony PlayStation 3 (PS3) as well as IBM Blade servers where are two processors on one board, building block. There can be more boards connected in one system forming a powerful and modular machine. We have two PS3 machines available for this work.

# **Chapter 3**

# **Cell/B.E. programming**

Cell/B.E. platform development tools will be described in this chapter. Our experience with the tools will be mentioned as well. Then particular SDK content and tools will be listed. Parallel systems and models will be mentioned later on as well as the relationship to the Cell/B.E. development along with a few design patterns. At the end core configurations and their advantages and disadvantages will be listed finishing with few practical approaches to the Cell/B.E. porting process.

### 3.1 Cell/B.E. platform development

IBM delivers a SDK for the Cell/B.E. application development. It is made for a Linux platform, in the concrete for the Fedora or the Red Hat distribution. It comes in two flavours. The first is the official non free SDK which has all the features needed for the Cell/B.E. development even for hybrid systems. The purchaser has also a support team ready to help. The next is a free one that is open to wide public and everybody can download it and start developing. The free one does not have full support for hybrid systems nor for development in other languages than C/C++. We have used the free one since we have developed only in C/C++ and for a clean Cell/B.E. processor.

Because the SDK is for Linux operation system its user has to have already a deeper knowledge about this system. There are a few bugs and parts that are not fully finished (see Appendix B) and without the deeper system knowledge is practically impossible to react on an unexpected behaviour during installation or development phase.

We have begun with SDK version 3.0 and Fedora version 8 which were the current versions of needed tools. We have faced a number of obstacles and before we were able to overcome them a new version of SDK (3.1) appeared. Because we

wanted to use and describe the latest tools we had to begin from scratch because the new version brought new obstacles as well.

The new version was declared to be compatible with a new version of Fedora, 9 - Sulphur, that had been released at almost the same time as the new SDK version. The previous version of SDK (3.0) was for Fedora 7 Werewolf. We have tried all possible combinations of Fedora distributions and SDK packages to find out if they are compatible with each other. The only result from that testings was finding out that they are not mutually compatible. We have spent plenty of days on this discovery. The SDK is a huge package of software dependent on lots of third party libraries and solutions. They are treated differently within particular distributions and sometimes even versions of the same distribution. The resulting advise is to avoid combination of system versions nor SDK versions nor particular libraries that the SDK components are dependent on. The repository versions of the third party software should be used.

Although there are too much of troubles when different version are combined, a few efforts to get the SDK run on another distributions than Fedora were made. But we think the time spent on this goal is not worth the result.

Finally we installed Fedora 9 Sulphur and SDK 3.1. Although this combination is declared by IBM as tested we have run into few bugs and errors. The process of installation is described in the Appendix B.

### 3.2 SDK content

The Cell/B.E. SDK is divided into variety of components. Each component is contained in one or more rpm package for easy installation purposes. Here is a list of important available components:

1. Tool chain

Is a set of tools such as compilers, linkers etc. necessary for actual code generation. There are two tool chains. One is for PPU and the other for SPU.

2. Libraries

IBM provides several useful libraries for mathematical purposes e.g. linear algebra, FFT, Monte Carlo with the SDK. Another libraries set is for cryptography or SPE run-time management. Code of these libraries is debugged, highly optimized for running on SPEs and SIMDized. It is highly advisible to use the libraries i.e. adapt a code for using the libraries instead of programming own solution.

3. Full system simulator

Program that can simulate the Cell/B.E. processor on other hardware platforms. It is used mostly in profiling stage because simulator can simulate actual computation of a code in cycle precision. It can be of course used when programmer has an actual Cell/B.E. hardware available, but the simulation is incredibly slow.

4. IDE

IDE is in fact version 3.2 of Eclipse with integration of debugging, profiling, Cell/B.E. machine management and other features that makes development for the Cell/B.E. easier and more comfortable.

### **3.3 Parallel systems & Cell/B.E.**

Parallelism depends on type of system where the program will be run. There are two basic kind of parallel systems:

1. shared-memory system

Is a multi-processor system with one shared memory which all processor can see. Processors has to synchronize access to the memory otherwise race conditions will rise.

2. distributed-memory system

Is system where each processor has its own private memory. There is no need for any synchronization.

In context of parallel systems Cell/B.E. is a kind of hybrid system. The SPEs matches a distributed-memory system due to private local stores while the PPE is a shared-memory system. The Cell/B.E. is sometimes called heterogeneous multi-core processor with distributed memory. Because Cell/B.E. processors can be composed into bigger units such as IBM blade server with two Cell/B.E. chips they can be viewed as either 16 + 2 cores in SMP mode or two non-uniform memory access machines connected together. Programmer has then to decide which view of the Cell/B.E. processor is better for the solved problem.

Because of separation of address spaces programming of the SPE is very similar to client/server application design. Roles depends on how the work is started. In case the PPU initiates the transfers, the PPU is a client and the SPE is a server because the SPE receive data for computation and offer a service for the PPE. Another possibility is that the SPE grabs the data from the central memory. In this case the SPE is a client of central memory. This scenario is preferred because the PPE is only one and would not be able to manage all the SPUs.

### **3.4 Cell/B.E. programming models**

Implementation of parallel algorithms rely on a parallel programming model. It is a set of software technologies such as programming languages extension, special compilers, libraries through that actual parallelism is achieved. The programming model is programmer's view to the hardware. Choosing a programming model or mixture of models that will best fit for the solved problem is another decision that programmer has to make.

For the Cell/B.E. there is variety of parallel programming models. THe models differ in view of the hardware from each other and thus how many actions are performed implicitly by the model. The actions can be e.g. task distribution management, data distribution management or synchronization. The most abstract ones can perform many actions implicitly. Their advantage is ease of implementation but at cost no performance tuning ability. Differently act the most concrete models that see the Cell/B.E. processor with all the low level details. Their advantage is performance tuning ability in all application parts but at cost of more development.

There are several models that are targeted only for the Cell/B.E. platform and are contained in the SDK. While there are other models such as MPI, OpenMP that can be used as well but they would expose only the PPE. These will not be further described.

List of the programming models (frameworks) follows in order from the most concrete to the most abstract:

1. libspe2

This library provides the most low level functionality. It offers SPE context creating, running, scheduling or deleting. DMA primitives for data transfer, mailboxes, signal, events, and synchronization functions for PPE to SPE and SPE to SPE dialogues are also provided by this library. More information can be found in [7] within "SPE Runtime Management Library" document.

2. Data Communication and Synchronization - DaCS

Defines a program entity for the PPE or the SPE. It is a HE (Host Element program) for the PPE and an AE (Accelerator Element program) for the SPE. It provides variety of services for that programs. The services are e.g. resource and process management where an HE manipulates its AEs or group management, for defining groups in which synchronization events like barriers can happen or message passing by using send and receive primitives. More information can be found in [7] within "DACS Programmer's Guide and API Reference" document.

3. Accelerated Library Framework - ALF

The ALF defines an ALF-task as another entity that perform computationally intensive parts of a program. The idea is to have a program split into multiple independent pieces which are called work blocks. They are described by a computational kernel, the input and the output data. Programming with the ALF is divided into two sides. The host and the accelerator one. On the accelerator side the programmer has only to code the computational kernel, unwrap the input data, and pack the output data when the kernel finishes. The ALF offers clear separation between the host and the accelerator sides of program parts. It provides following services: work blocks queue management, load balancing between accelerators, transparent DMA transfers etc. More information can be found in [7] within "ALF Programmer's Guide and API Reference" document.

Choosing a framework is important decision of writing Cell/B.E. application. It should be considered enough.

#### 3.4.1 Cell/B.E. parallelism levels

The Cell/B.E. processor offers four levels of parallel processing. That is because it is composed of heterogeneous elements, the SPE and the PPE and the possibility of composition into a more complex systems. The levels are:

1. Server level

Parallelism on this level means task distribution among multiple servers like within a server farm. This is possible in a hybrid environment at the cluster level using MPI or some other grid computing middle-ware.

2. Cell/B.E. chips level

On this level tasks can be divided among multiple Cell/B.E. processors. This is possible if there are more such processors in single machine. It is e.g. IBM Blade server with two Cell/B.E. chips. ALF or DaCS for hybrid can be used for task distribution.

3. SPE level

This parallelism level allows to distribute tasks among particular SPEs. Libspe, ALF, DaCS can be used to perform the distribution.

4. SIMD instruction level

This level can increase the speed the most. Parallelism is achieved on instruction level that means more data are processed at a time by single instruction. Language intrinsics are used for this purpose. This will be explained later in part devoted to "SIMDation".

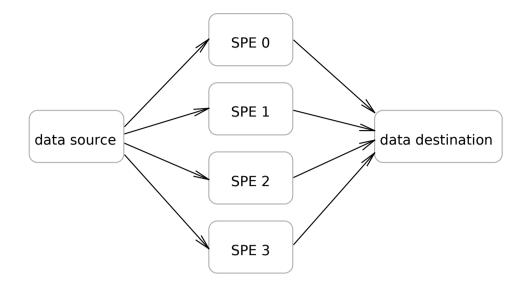

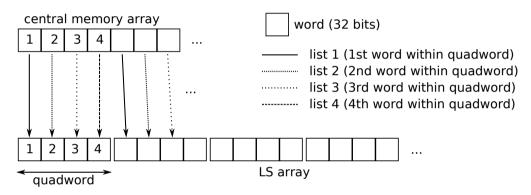

Figure 3.1: All SPE run the same code creating farm of processor that process same type of data.

#### 3.4.2 Computation configurations

Because of the Cell/B.E.'s heterogeneous nature there are few computation configurations that can be used. Each of them differs in usage of SPEs:

1. Streaming configuration

All SPEs serves as a stream processor (see figure 3.1). They run exactly the same code expecting the same type of data and producing also the same of data type. This configuration is well suited for streaming application for example filters where there is still the same type of data on input.

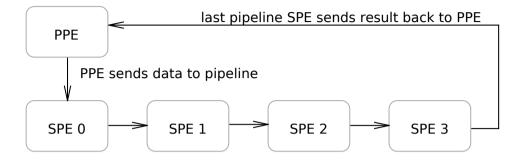

2. Pipeline configuration

The SPEs are stages of a pipeline (see figure 3.2). Data are passed through one SPE to another. This configuration makes use of the fact that transfer among SPEs is faster than the transfer between SPE and PPE.

3. PPE centric

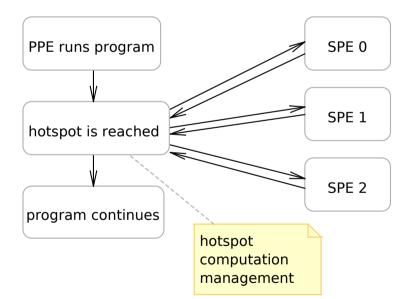

This configuration is common approach to use the Cell/B.E. A program runs on the PPE (see figure 3.3) and only selected, highly computational intensive parts (hotspots) are offloaded to SPEs. This method is the easiest from a program development perspective because it limits the scope of source code changes and does not require much re-engineering at the application logic level. A disadvantage is frequent changes of SPE contexts that is quite expensive operation.

Figure 3.2: SPE creates a pipeline. Each SPE represent one stage of that pipeline. Data are transferred only via SPE to SPE DMA transfers benefiting the speed of bus.

Figure 3.3: Program is run on PPE and only hotspots are offloaded to SPEs. Offloading means managing SPE context creation and loading as well as managing data transfer and synchronization between PPE and SPEs

4. SPE server

Another configuration is to have server-like programs running on SPEs that sits and waits offering specific services. It is very similar to the PPE centric configuration. Only difference is requirement to the program to be small enough to fit into the SPU local store to avoid the frequent SPE context switching.

### **3.5** Building for the Cell/B.E.

Actual compilation process is performed using an appropriate tool chain. The PPE code requires the PPE tool chain and the SPE code requires the SPE one. But there is a difference between management of the code in linking stage between the PPE and the SPE object files. It is caused by difference of actual code usage. While the PPU code resides in the central memory, like in common architectures, the SPU code is loaded into the SPE dynamically and shall be somehow separated from the PPE code. It is similar to shader programs for graphic accelerators. They are also loaded into appropriate processors as soon as they are needed so they live separated.

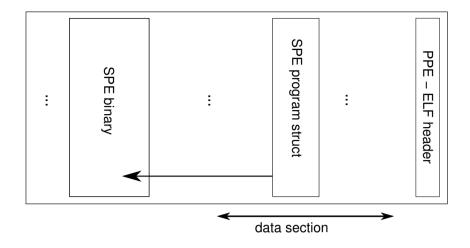

There are two options for SPE code management. One is to build a shared library and load it explicitly when it shall be used. Another way is to build a static library and include it into the PPU executable using Cell/B.E. Embedded SPE Object Format (CESOF). This allows PPE executable objects to contain SPE executable i.e. the SPE binary is embedded within the PPE binary, see figure 3.4. The SPU program is then referenced as special external structure directly from the PPU code instead of performing shared library loading. Both ways have advantages and disadvantages which are the same as shared vs. static library usage. Shared library means better modularity and possibility of code alternation without whole executable rebuilding. On the other hand additional management of such library is necessary in contrast to a static SPE code into a PPE binary embedding.

#### **3.5.1 Process of application porting for the Cell/B.E.**

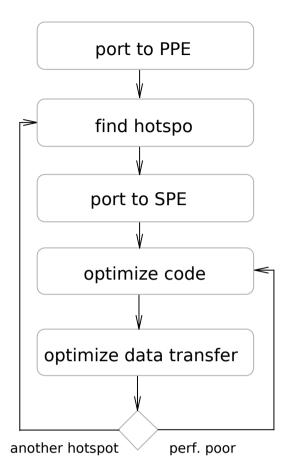

Common process of application porting for the Cell/B.E. processor (figure 3.5) consists of next two basic steps:

1. Hotspots localization

Through profiling of the application on the PPE we find most compute intensive parts, hotspots. How to profile the application see chapter 5 of [5].

Figure 3.4: Illustration how is a SPE binary "embedded" into a PPE binary. The SPE binary is another section of the PPE binary. It is reachable through extern struct variable, that contains a pointer to the SPE binary.

2. Hotspot porting for SPE

Each hotspot computation is moved to the SPE i.e. the code adaptation for the SPE features shall be performed. This means DMA transfers instead of direct memory access, appropriate data structures utilization, etc. Data movement tuning e.g. different data structures usage can be then performed until satisfactory performance is obtained.

Work distribution among available SPEs shall be performed to accelerate actual computation. Amount of work performed by particular SPEs should be equal to avoid mutual SPE waiting.

Following additional steps are necessary for application optimization and speedup. Performing these steps leads to utilization of all the SPU features such as whole register set utilization, dual-issuing of instructions, SIMD execution and DMA transfers. More detail in [4], part 4:

1. Multi-buffering

Data that resides within central memory and are processed by the SPE should be copied into local store before actual computation. When there are more of the places for the data (buffers) the program can take advantage from asynchronous DMA transfer and can process current buffer while the next data are being transferred into another buffer. Then the buffers are simply swapped and the SPU need not to wait until the transfer of next data is complete. See the figure in the paragraph named "Hiding data-access latencies" in [17] for illustration.

2. Branch elimination

Branch less instruction chain is a succession of instructions without any conditional jump. In other words there is no decision where to continue performed within such succession. Elimination of branches elongates the branch less instruction chain. In such a chain all data always go through the same instructions which makes possible to perform SIMDation. There is variety of branch elimination methods. Good information resource provides [1]. Branch elimination is probably the most complicated step due to necessity of complete code restructuralization.

3. SIMDation

Means rewriting a scalar code into a vectorized one to be able to use SIMD instructions. In this step the most performance gain could be achieved because of multiple data processing by one instruction. Every single piece of data should go through the exactly same order of instructions in SIMDized code. Therefore is necessary to have long branch less instruction chain. The most important method is arrays of structure to structure of arrays conversion. The figure in the paragraph called "SIMDizing" in [17] shall illustrate the data processing with SIMD instructions.

SIMDizing brings also avoidance of usage a rotation instructions which are necessary to move unaligned data into preferred slot. Preferred slot is the beginning of a register e.g. for short integer it is the first 16 bits of the register.

4. Loop unrolling

Loop body is the code inside curly brackets of the loop. This code is executed repeatedly until the loop condition is valid. Loop unrolling means putting more loop bodies serially into the code. This decrease loop count and elongate the loop body letting the compiler to make more optimizations. Example:

```

for(uint32 i=0; i<32; i++)

{

printf(".");

}</pre>

```

become (by loop unrolling with factor 2)

```

for(uint32 i=0; i<16; i++)

{

printf(".");

printf(".");

}</pre>

```

The compiler can do more optimizations e.g. better instruction scheduling and register utilization.

Figure 3.5: Diagram shows all stages of the process and loops for better performance tuning and other hotspots

5. Instruction scheduling

Proper reorganization of instructions can give more performance in some cases. This step is performed by the compiler but it is possible to rearrange instructions manually in assembly language.

6. Branch hinting

Gives a hint where the program is rather going to continue after future branch to the processor. It is done through insertion of special instructions. This step should be again accomplished by the compiler but it is possible to use appropriate assembly language instruction directly within the code.

### 3.5.2 SPE porting considerations

The local store size is the main SPE feature that everything spins around while porting a code to the SPE. On the one hand there are decisions about data transfers.

This means how the data that has to be processed by the SPE will be transferred into local store and vice versa. How many buffers will be used in case of multi-buffering. On the other hand is code complexity of the solved problem that influence the size of the final binary. There is one solution how to use bigger binaries than the local store, SPE overlays. It is based on division of the binary into segments that are loaded into the SPE on demand in run-time.

Programmer has to take into consideration all these things to make the final binary smaller than the local store. Everything is big trade-off between the processed data chunk sizes, number of buffers for that chunks and the code lenght.

After the first compilation of a SPU binary from original ported code the final executable will probably exceed the local store size even when the code does not seem as large. Then a big searching what part of code causes the huge size would begin. We have gone through several problems with code that is common in non SPE code but cause problems in the SPE code. Here is the list:

1. usage of keyword new

There is no memory allocation in the SPE. So usage of the *new* keyword is meaningless. But the SPE compiler accepts it without any complain.

2. usage of std streams

This code:

#include <iostream>

std::cout << "Hello" << std::endl;</pre>

goes through the compiler without complaints but makes the final binary very big.

The reason why the resulting code is too big is probably size of the code within headers that are included when using described features.

#### **3.5.3** Speed and compiler options

There is variety of compiler options. Usage of them is worth nothing but can increase performance and avoid some kind of bugs.

Mike Acton explains strict aliasing in [2]. One advantage of usage of this feature is positive impact on performance. Another advantage is fact that it can avoid bugs that would appear as far as in release stage when optimizations flags are used during compilation. In this stage is really hard to track and debug this kind of bugs.

```

Another option advises are in [17]

```

## 3.6 Profiling

Profiling of Cell/B.E. application means rather profiling the SPE part of the application. There is variety of profiling tools. The basic one is a dynamic performance analysis which can provide many useful information such as how much time SPE stalled, reasons of the stall, the CPI (cycle per instruction) ratio, branch count, etc. The next one is a static performance analysis which can illustrate run of a SPE in instruction precision. These two analysis are evaluated from program run within full system simulator. Both the methods are well described in tutorial in the cell IDE help which is accessible through menu  $\rightarrow$  Help  $\rightarrow$  Help Content in the IDE.

Another profiling tools are:

- 1. PDT performance debugging tool

- 2. OProfile

- 3. CPC cell performance counter

These tools collect profiling data that can be further processed with VPA (visual performance analyser), an external tool provided by IBM. This tool can display the collected data in different charts, time lines or can highlight parts of the code that are worth to improve and many other useful features. Usage of all these performance tools is described in SDK document "Performance Tools Reference" in [7]. We wanted to test them all but when we followed the manual instructions we experienced a few obstacles because we worked on PS3. Lately, we have found out on forums that unfortunately there is poor or none support for these performance tools on PS3.

# **Chapter 4**

## **Image segmentation**

Image segmentation will be described in this chapter as well as several basic segmentation techniques. Subsequently level set techniques will be introduced, defined and explained in more detail. Then level set computation issues will be described along with mentioning of two basic speed-up approaches. After that level set method relation to image segmentation will be mentioned. After all some features of the level set computation on streaming architectures will be listed along with comparison to the Cell/B.E. features.

## 4.1 **Problem formulation**

Image segmentation is process when pixels of an input image are split into several subsets, segments, based on their characteristics or computed properties, such as colour, intensity, or texture. The pixels in such segments have similar features and compose an object in the image.

In more formal way it is a function that assign a segment to a pixel:

$$S:S(p) = k \tag{4.1}$$

where  $p \in \text{pixels}$  of the image and  $k \in \text{set}$  of segments.

Image segmentation is used in many domains such as medicine (locating organs, tumors, bones, etc.), satellite images classification for maps (location buildings, roads, etc.), machine vision (fingerprint recognition, face, eyes, or other features recognition). Other example of image processing application can be a simple tool as the well known "magic-stick" tool in popular graphics editing software like Photoshop. Although there were some attempts to find general-purpose segmentation solution, results were not satisfactory. So there is not yet a general solution. Each domain needs extra approach how to perform the segmentation. Some of them are not even fully automatic so they need assistance of an operator. They are called semi-autonomous approaches. These methods need an operator who inputs some region and thus gives a hint to the algorithm. This is favourite approach in segmentation of structures in medical images like organs, tumors, vessels, etc. A physician then plays the role of the operator because of his knowledge of images' content. Some methods are autonomous but need some apriory knowledge of the segmented object properties.

### 4.2 Image segmentation methods overview

Image segmentation methods can be divided into following basic categories (information based on [19]):

1. Clustering

These methods are used to partition an image into N clusters that cover the entire image. Two main subsets of the methods are bottom-up and top-bottom. The first one takes each pixel as separate cluster and then iterate joining these initial clusters based on some criterion until there are N clusters. The second one picks N randomly or heuristic chosen cluster centres. Then these two steps are repeated until some convergence condition is met e.g. no pixels change clusters: assign pixels to clusters based minimalization of the variance between the pixel and the cluster centre and re-compute the cluster centres by averaging all of the pixels in the cluster.

2. Histogram-based

Firstly a histogram is computed from pixels of the image. Then peaks and valleys in the histogram creates the segments in the image. Result can be refined by recursively repeating the process. The recursion is stopped when no more new segments appear.

3. Edge detection

These methods segment an image based on its edges. Therefore core of such methods is an edge-detection algorithm such as Canny, Sobel.

4. Region growing

This set of methods are very similar to the flood-fill algorithm. It takes a set of seed points and a segmented image. Each seed point is something like pointer to segmented object on the image. Seed points form an initial set of segments. Then iteration through the neighbouring pixels of the segments is performed. In every step of that iteration a neighbour pixels of a segment is compared with the segment i.e. similarity function is calculated. If the pixel is considered similar enough it is added to the segment. Method is highly noise-sensitive. The initial seeds can be misplaced due to the noise. Therefore there is another algorithm that is seedless. It starts with a single pixel that is an initial region. Its location does not significantly influence the final result. Then the iteration over the neighbouring pixels are taken just as in seeded growing. If a neighbour is different enough new segment is created. A threshold value is used as similarity measurement but particular approaches differs in definition of the similarity function. While one group uses pixel's properties like intensity or colour directly another computes some statistical test from the properties and the candidate pixel is processed according the test is accepted or rejected.

5. Graph partitioning

This approach converts an image into a graph. The pixels correspond to the vertices. There is edge between every pair of the pixels. Edges are weighted with similarity function of the two connected pixels. Then a graph algorithm that cuts off edges is run partitioning the graph resp. image. Popular algorithms of this category are the random walker, minimum mean cut, minimum spanning tree-based algorithm, normalized cut, etc.

6. Watershed transformation

The watershed transformation considers the gradient magnitude of an image as a topographic surface. Pixels having the highest gradient magnitude intensities correspond to watershed lines, which represent the region boundaries. Water placed on any pixel enclosed by a common watershed line flows downhill to a common local intensity minimum. Pixels draining to a common minimum form a catch basin, which represents a segment.

7. Model based segmentation

The main idea of this method is to describe the segmented object statistically, constructing a probabilistic model that explains the variation of the object shape. In segmentation phase is the model used to impose constraints as prior. Searching for such model contains steps like: registration of the training examples to a common pose, probabilistic representation of the variation of the registered samples and statistical correspondence between the model and the image.

8. Level set

It is a method that uses a mathematical model of the segmented object. It is represented by a level set function. Segmentation is performed by deformation of an initial isoline (for 2D case), hyperplane of the level set function, with forces that are computed from the segmented image.

Figure 4.1: An initial shape, the circle, grows and floods the object on the background. In contrast to common flood-fill approach, level set method has several parameters that can e.g. prevent flooding beyond the object borders through small holes.

Whole process can be illustrated in very similar way to the flood-filling, see the figure 4.1. The initial isoline is deformed with forces that has direction of an isoline normal. For 2D case the initial isoline can be e.g. a simple circle as a hyperplane of a distance function from a given point. When it approaches object borders the propagation slows down. On the object borders the propagation stops because the forces are zero there.

Another illustration uses a landscape with a lake. Water is always at a constant altitude and the surface of the landscape changes in time. With the changes of the landscape the shoreline of the lake changes as well. The landscape represents the level set function and the water surface represent the isoline i.e. k-level set.

Advantages of the level set method are lack of special treatment of merging and splitting surfaces necessity, few intuitive parameters, ability of topology changing. The most suiting advantage for our purpose is ability of performance in all dimension without explicit changes in method because we will perform volume segmentation i.e. 3D case of level set.

## 4.3 Level set

Level set method as proposed by Osher and Sethian [15] provides numerical and mathematical mechanisms for surface deformation computation as time varying isovalues of level set function using partial differential equations (PDE).

#### 4.3.1 Level set theory

Information in this and following paragraphs are based on [20] and definitions will be for 2D case. The level set function is a signed scalar distance function

$$\phi: U_{x,y} \to \mathbb{R},\tag{4.2}$$

where  $U \subset R^2$  is the domain of the function.  $\phi$  is called embedding and is implicit representation of the segmented object. Isoline is then a subset of the level set function values, a hyperplane

$$S = \{\vec{x} \mid \phi(\vec{x}) = k\} \tag{4.3}$$

The symbol *S* represents a *k*-isoline or *k*-level set of  $\phi$ . The variable *k* can be chosen freely, but in most cases it is zero. The isoline is then called zero isoline, zero level set or dimension insensitively front (will be used further).

Deformation of the front is then described by an evolution equation. One approach, dynamic, uses one-parameter family of  $\phi$  function i.e.  $\phi(\vec{x},t)$  changes over time,  $\vec{x}$  remains on the *k*-level set of  $\phi$  as it moves and *k* remains constant. Resulting equation is

$$\phi(\vec{x}(t),t) = k \Rightarrow \frac{\delta\phi}{\delta t} = -\Delta\phi \cdot \vec{v}. \tag{4.4}$$

Where *v* represents movement of a point *x* on the deforming front i.e. positions in time. All front movements depend on forces that are based on level set geometry which can be expressed in terms of the differential structure of  $\phi$ . So following version of equation 4.4 link formulated:

$$\frac{\delta\phi}{\delta t} = -\Delta\phi \cdot \vec{v} = -\Delta\phi \cdot F(\vec{x}, D\phi, D^2\phi, ...), \qquad (4.5)$$

where  $D^n \phi$  is the set of *n*-order derivatives of  $\phi$  evaluated at  $\vec{x}$ . The term  $F(\vec{x}, D\phi, D^2\phi, ...)$  represents the force that influence the movement of a surface point. This equation can apply to every values of *k* i.e. every level set of function  $\phi$  and is basic equation of level set method.

#### 4.3.2 Level set computation

Computation of surface deformations has to be discretized which means it is performed on discretized space i.e. grid. Front propagation is then computed from initial model in cycles representing discrete time steps using this update equation:

$$\phi_{i,j}^{n+1} = \phi_{i,j}^n + \Delta t \Delta \phi_{i,j}^n, \qquad (4.6)$$

where the term  $\phi_{i,j}^n$  is discrete approximation of  $\frac{\delta\phi}{\delta t}$  referring to the *n*-th time step at a discrete position *i*, *j* which has a counter part in continuous domain  $\phi(x_i, y_j)$ .

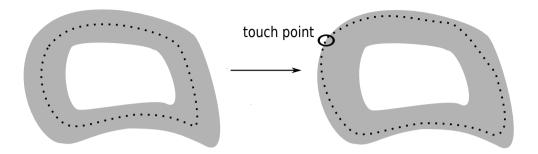

Figure 4.2: Embedding computation is performed only within narrow band (highlighted in grey). When level set touches (highlighted by the circle) the border or the band, new band has to be computed i.e. reinitialized.

$\Delta t \Delta \phi_{i,j}^n$  is a finite forward difference term representing approximation of the forces influencing the level set, the update term. The solution is then succession of steps where new solution is obtained as current solution plus update term.

Discretization of the level set solution brings two problems. Fist one is need of stable and accurate numeric scheme for solving PDEs. This is solved by the 'upwind scheme' proposed by Osher and Sethian [15]. The second one is high computational complexity caused by conversion problem one dimension higher. Straightforward implementation via *d*-dimensional array of values, results in both time and storage complexity of  $O(n^d)$ , where *n* is the cross sectional resolution and *d* is the dimension of the image. In case of pictures with size about 512<sup>3</sup> voxels the level set computation takes very long time.

#### 4.3.3 Speed-up approaches

Because of computational burden of straightforward level set solving some speedup approaches has been proposed. They are useful only when only single level set is computed which is the case of image segmentation. Then is unnecessary to compute solution for given time step over whole domain but only in those parts that are adjacent to the level set. Beside the most known and used Narrow Bands and Sparse Fields there is an octree based method proposed by Droske et al. [9].

Narrow Band, proposed by Adalsteinsson and Sethian [3], computes embedding only within narrow band, tube. Remaining points are set constant to indicate that they are not in the tube. When level set reach the border of the tube, a new tube has to be calculated based on current level set. Then new run of computations are performed on this new tube until involving level set reaches tube borders again or the computation is stopped.

#### CHAPTER 4. IMAGE SEGMENTATION

Sparse Fields method, proposed by Whitaker [18], introduces a scheme in which updates of an embedding are calculated only on the level set. This means that it performs exactly the number of calculations that is needed to calculate the next position of the level set. This is the biggest advantage of the method.

Points that are adjacent to the level set are called active points and they form an active set. Because active points are adjacent to the level set, their positions must lie within certain range from the level set. Therefore the values of an embedding in active set positions must lie on certain range, the active range.

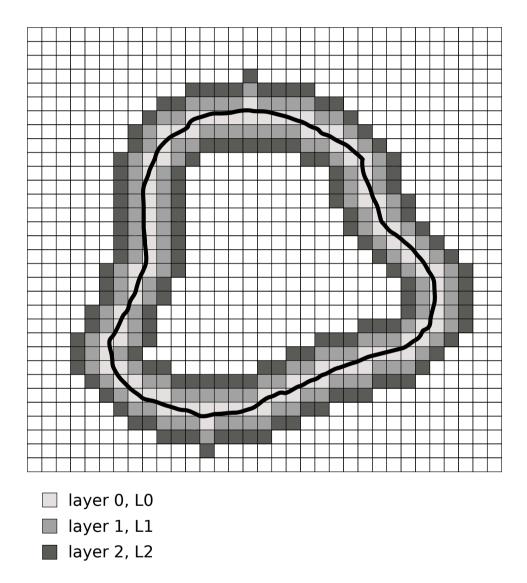

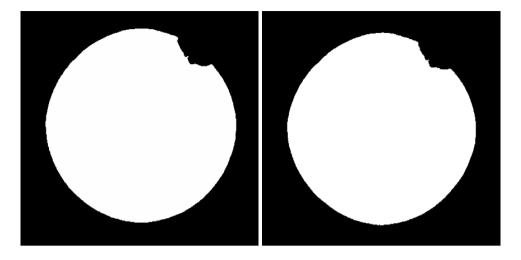

When active point value move out from the active range, it is no longer the active point and is removed from the active set. And vice versa, the point whose value comes into active range is added into active set. Along the active set there are few layers of points adjacent to the active set organized like peels of an onion, see the figure 4.3.

Process of front propagation can be imagined as a tram that lays down tracks before it and picks them up behind.

Algorithm (from [20]):

*layer*,  $L_i$  - set of points that are close to the level set. *i* is order of a layer, negative for inner layers, positive for outer ones. Zero is for the active set layer. See the figure 4.3

statuslist,  $S_i$  - list of points within *i*-th layer that are changing status

DO WHILE (stop condition is met):

1) FOREACH (point  $\in$  active set, the zero layer (ZL) a) compute level set geometry  $(\vec{x})$

b) compute change using the upwind scheme in point  $(\vec{x})$

2) FOREACH (point  $\in$  active set compute new embedding value  $\phi_{i,j,k}^{n+1}$ , which means computing 4.6.

Decide if it falls into  $[-\frac{1}{2},\frac{1}{2}]$  interval. If  $\phi_{i,j,k}^{n+1}$  moved under the interval, put the  $(\vec{x})$  into lower status list, resp. into higher if  $\phi_{i,j,k}^{n+1}$  moved above the interval.

3) Visit points in other layers  $L_i$  in order  $i = \pm 1, ..., \pm N$ , and update the grid point values based on the values of the next inner layer  $L_{i\pm 1}$  by adding resp. subtracting one unit.

If more than one  $L_{i\pm 1}$  neighbour exists then use the neighbour that indicates a level curve closest to that grid point. i.e. use the point with maximal value for the outside layers resp. point with minimal value for the inside ones. If a grid point in layer  $L_i$  has no  $L_{i\pm 1}$  neighbours, then it gets denoted to the next layer away from the active set,  $L_{i\pm 1}$ .

Figure 4.3: Embedding is calculated only at points that are covered by the level set (the white line). Those points (active set) are coloured in black forms the zero layer. Other layers embrace the zero layer from both inner and outer side, formed like onion peels

4) For each status list  $S_{\pm 1}, S_{\pm 2}, ..., S_{\pm N}$  do the following:

a) For each element  $x_j$  on the status list  $S_i$ , remove  $x_j$  from the list  $L_{i\pm 1}$  and add it to the  $L_i$  layer. Or in the case of  $i = \pm (N+1)$ , remove it from all layers. b) Add all  $L_i$  meighbours to the  $S_i$  list

b) Add all  $L_{i\pm 1}$  neighbours to the  $S_{\pm 1}$  list.

The stop condition is specified by maximal count of iterations. Another stopping criterion is based on a measurement of the front movement. When the front does not move anymore, calcultation is stopped before maximal count of iterations is reached.

#### 4.3.4 Level set image segmentation

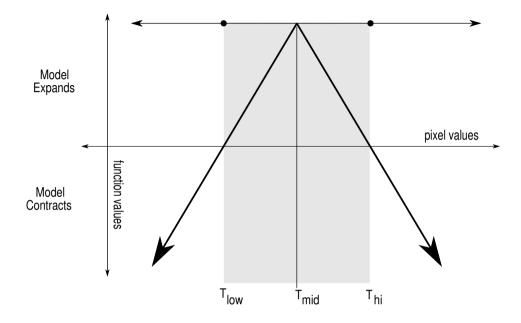

Image segmentation using a level set method is performed based on a speed function that is calculated from the input image and that encourages the model to grow into directions where the segmented object lies. There is variety of the speed functions. In this work we used speed function based on a threshold  $T_{low}$  and  $T_{hi}$  of the intensities if pixels from the input image. If a pixel has intensity value that is within the threshold interval the level set model grows, see the figure 4.4. Otherwise it contracts as fast as the pixel has value further from the interval. The function D is defined as:

$$D(\vec{x}) = \begin{cases} V(\vec{x}) - T_{low} & \text{if } V(\vec{x}) < T_{mid} \\ T_{hi} - V(\vec{x}) & \text{if } V(\vec{x}) > T_{mid} \end{cases}$$

(4.7)

where  $V(\vec{x})$  is pixel value in point  $\vec{x}$  and  $T_{mid}$  is the middle of the thresholding interval.

This is quite natural definition of what we need from the process i.e. grow as fast as possible where the segmented object lies and contract otherwise.

The update term from equation 4.6 can be rewritten into following form that consist of few terms:

$$\phi_t = \alpha |\bigtriangledown \phi| H + \beta \bigtriangledown |\bigtriangledown I| \cdot \bigtriangledown \phi + \gamma |\bigtriangledown \phi| D \tag{4.8}$$

where  $| \bigtriangledown \phi | D$  represents speed function term,  $\bigtriangledown | \bigtriangledown I |$  is edge term that is and  $| \bigtriangledown \phi | H$  represent curvature term.  $\alpha$ ,  $\beta$  and  $\gamma$  are weights of particular terms.

Edge term is computed from second order derivatives just like Canny and Marr-Hildreth algorithms for edge detection. It shall to push level set towards edges, i.e. border of segmented object.

Curvature forces the resulting level set model to have less surface area and thus protect negative effects like leaking into unwanted places shown in the figure 4.5. Note: if  $\alpha = \beta = 0$ , the result is the same as flood-fill method result because there is only the speed term taking place in the calculations.

Figure 4.4: Gray rectangle encloses interval where the speed function is positive, i.e. the model expands. The fastest expansion is in the  $T_{mid}$  point

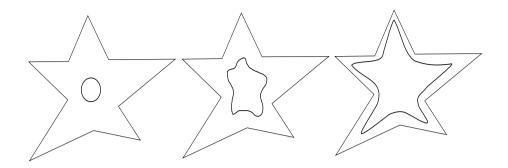

Figure 4.5: Illustration of leaking artefacts. Initial level set - circle (left). Without curvature forces, segmentation leaks into unwanted places (center). Segmentation with curvature forces (right).

We omitted the edge term so there are only two parameters in our method. Tuning of the term weights has to be performed in order to have the best results.

#### **4.3.5** Level set methods on streaming architectures

There were some attempts for porting level set method onto special stream device. There are some obstacles due to streaming architecture that has to be overcomed to efficiently solve the problem. Firstly the streams of data must be large, contiguous blocks in order to take advantage of streaming architecture. Thus the points in discrete grid near the level-set surface must be packed into data blocks that can be further processed by streaming processors. Another difficulty is that the level set moves with each time step, and thus the packed representation must be quickly adapted.

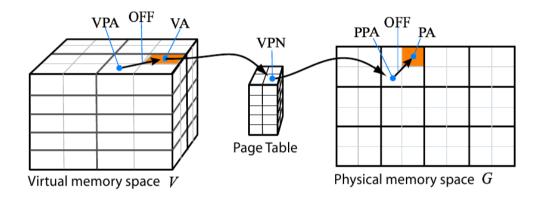

For example Cates at al. [11] or Lefohn at al. [13] ported level set segmentation method to GPU. GPU is a streaming architecture with many, nowadays hundreds, of streaming cores. They run short programs called shaders. In porting to GPU architecture a texture memory is used to store input data in a large continuous block. Actual computation is then managed by vertices that flow into the shader and play a role of pointers to the texture memory. This is some kind of trick because the texture memory is not addressed directly by address number like in single dimension continuous address space in common processors but instead by a 2D coordinate vector. Because vertices comes as 3D points, virtual memory system that map 3D vertices to 2D texture coordinates has to be created. Such system proposed Lefonh at al. [13]. See the figure 4.6.

Another workaround has to be performed when computed data is transferred back to the CPU. This direction is much slower than the CPU to GPU direction and thus the results has to be somehow packed. Lefonh at al. [13] describes this packaging as well. There are although some advantages. One is the high count of the processors and extreme fast dedicated memory so the results can be impressive. Another is that the calculation can be directly visualized by the GPU.

Although the Cell/B.E. has some parts of the approach in common with GPU it need not to overcome the GPU obstacles. For instance no virtual memory system need to be implemented because the SPE has its own flat address space by default. Also the result packing for sending back to CPU is not necessary because transmission of data from and to SPE has the same speed and can be performed directly. All these Cell/B.E. processor features could result easier and more straightforward process of porting of level set method. But speed of the Cell/B.E. result will not probably exceed the GPU solution speed.

Figure 4.6: Illustration of virtual memory system (taken from [13]). 3D space level set domain (that incoming vertices come from) is mapped via page table to 2D texture coordinate system.

# **Chapter 5**

# **Design and implementation**

This chapter will describe details of implementation and design of our test application. It will start with listing of used frameworks continuing with description of the process of the test application incorporation into the frameworks. After that results of profiling of the application will be summarized. Followed by a new design description which was necessary due to unexpected profiling results. The rest of chapter will present actual porting process with all its problems, solutions, recommendations and all the usable information that we discovered during the porting process.

## 5.1 Original idea of the porting process

We wanted to follow the common scenario of porting process as described in 3.5.1. In our case this means:

- 1. choose base implementation

- 2. clean it up

- 3. port it to PPE

- 4. profile it to find hotspots

- 5. offload hotspots to SPEs and right away to use multi-buffering technique for DMA transfers

- 6. optionally try some optimization steps if the results were not satisfactory

## 5.2 Chosen algorithm and frameworks

We decided to choose sparse field algorithm of level set solving for porting to Cell/B.E. It is a quite complex image processing algorithm that could test the Cell/B.E. programming as a whole.

We took ITK [12] implementation of the algorithm as a base. Therefore we had to get familiar with this huge project. It contains many algorithm implementations as well as necessary infrastructure content such as loading and saving variety of formats. The base concept of this project is a pipeline and filters.

To get some work done a pipeline has to be build from filters. Filter is an entity that represents an algorithm. When a pipeline is created the last filter is started. Starting event then propagates towards the beginning of the pipeline where actual computation starts. Output from one filter is input of the following one. Filters thus create a building blocks for a more complicated method.

After several first test with examples and tutorials we wrote our own testing application (originally with code name 'pok'). It was able load an image, run a level set filter and save the results. Some reasonable parameter values were found with the pok application. It was controlled via bash scripts that is not much easy nor user friendly solution. There was also no way how to visualize the results. Therefore we decided to use another framework to overcome these problems, the MedV4D project [16].